1、概述

i.MX 6ULL系列芯片的MMDC是一个多模式DDR控制器,支持DDR3/DDR3Lx16和LPDDR2x16的存储类型,MMDC是可配置,高性能,优化的内存控制器。

注:DDR3/DDR3Lx16、LPDDR2x16 ,此处的x16表示芯片位宽,每个传输周期能够提供的数据量(bit)。也就是说明,如果要提供32位的位宽内存存储,需要2颗以上型号的内存进行并联使用。

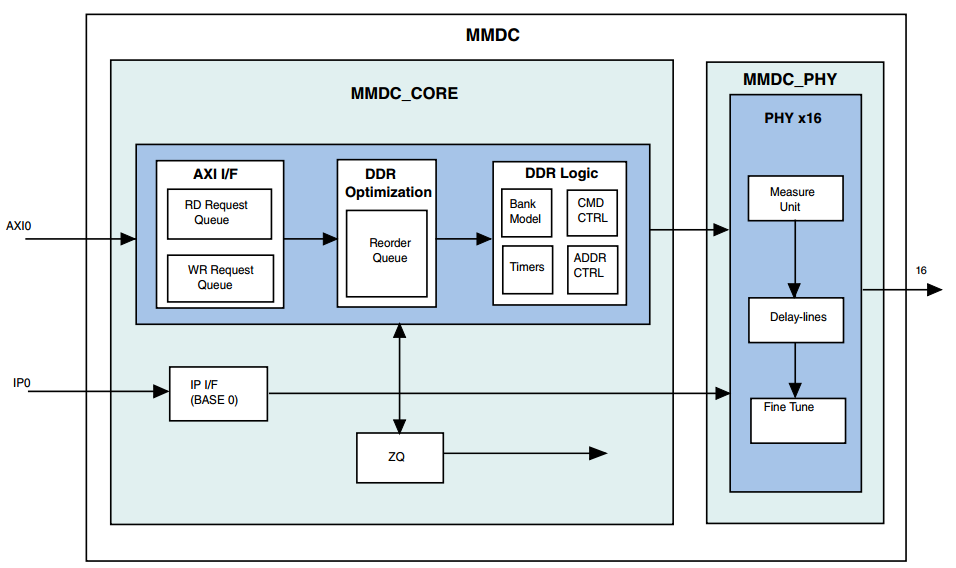

下面是MMDC逻辑框图:

- MMDC由内核(MMDC_CORE)和物理层(MMDC_PHYl)两部分构成。

- 内核负责通过AXI接口,DDR命令发生器,DDR命令优化器,和读写数据通道与系统通信,物理层负责定时调整,它使用特殊校准机制确保数据获取400MHz的时钟频率。

- MMDC的内部配置寄存器通过IP通道进行配置。

DDR标准:

- DDR3L,DDR3x16 LPDDR2x16

- 不支持LPDDR1MDDR 和DDR2

DDR接口:

- 16位数据总线宽度;

- 器件密度-256Mbits-8Gbits,其中列8-12bit,行11-16bit;

- 通过配置CS0,CS1可以达到4Gbyte地址空间;

- DDR3支持的突发长度为8;

- LPDDR2支持的突发长度为4;

DDR性能:

- 400MHz核心频率,800MHz数据频率

- 支持实时优先级,支持不同优先级的重新排序机制:实时,延时敏感,正常优先级

- 页面碰撞错过优化

- 连续读写访问优化

- 支持深度读写请求队列,支持bank预测

- 支持bank交叉

- ddr3模式下(突发长度)的非对齐换行访问情况下的特殊优化

AXI接口:

- 运行在400MHz,支持传输8/16/64 bits(单一访问和突发)

- 支持最大突发长度为16

- 支持16bits AXI ID

DDR通用设置:

- 可配置时序参数

- 可配置刷新周期

- 支持页边界交叉

- 支持LPDDR2 MRW和MRR指令

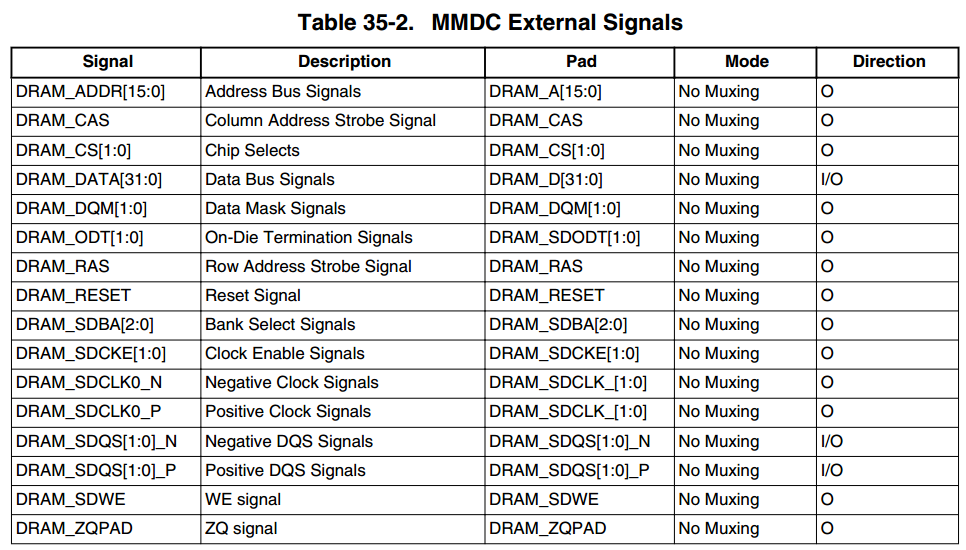

2、外部接口信号

3、时钟源

时钟设置参考CCM(clock controller module)模块

4、功能性说明

4.1 读/写数据流

4.2 MMDC初始化

4.3 配置MMDC寄存器

4.4 MMDC地址空间

4.5 LPDDR2与DDR3引脚复用映射

4.6 节能和时钟切换模式

4.7 复位

4.8 刷新计划

4.9 用于DDR的突发长度选项

4.10 独家访问处理

4.11 AXI错误处理

5、性能

5.1 仲裁和重新排序机制

5.2 预测机制

5.3 针对DDR3访问的特殊优化

6、MMDC 调试

7、 MMDC 剖析

8、LPDDR2刷新率更新和定时减量

9、DLL切换

10、ODT配置

11、校准过程

12、MMDC 内存映射/寄存器定义

参考资料:

https://blog.csdn.net/u011124985/article/details/81140819

IMX6ULLRM.pdf――恩智浦提供下载

https://baike.baidu.com/item/%E5%86%85%E5%AD%98%E6%9D%A1