S5PV210|S5PV210 ИХЪі

1.S5PV210 ИХЪі

-

1.1 МмЙЙИХЪі

S5PV210ЪЧвЛПю 32 ЮЛ RISC ИпадМлБШЁЂЕЭЙІКФЁЂИпадФмЕФЮЂДІРэЦїНтОіЗНАИЃЌЪЪгУгкЪжЛњКЭвЛАугІгУЁЃЫќМЏГЩСЫARM Cortex-A8ФкКЫЃЌЪЕЯжСЫARMМмЙЙV7-AЃЌжЇГжЭтЩшЁЃ

ЮЊ

3GКЭ3.5GЭЈаХвЕЮёЬсЙЉгХЛЏЕФгВМўЃЈH/WЃЉадФмЃЌS5PV210ВЩгУ64ЮЛФкВПзмЯпМмЙЙЁЃетАќРЈаэЖргУгкдЫЖЏЪгЦЕДІРэЁЂЯдЪОПижЦКЭЫѕЗХЕШШЮЮёЕФЧПДѓгВМўМгЫйЦїЁЃМЏГЩЖрИёЪНБрНтТыЦї (MFC) жЇГжMPEG-1/2/4ЁЂH.263КЭH.264ЕФБрТыКЭНтТыЃЌвдМАVC1ЕФНтТыЁЃ

ДЫгВМўМгЫйЦї (MFC) жЇГжЪЕЪБЪгЦЕЛсвщКЭФЃФтЕчЪгЪфГіЁЂгУгк NTSC ЕФ HDMI КЭ PAL ФЃЪНЁЃ

S5PV210ОпгагыЭтВПДцДЂЦїЕФНгПкЃЌФмЙЛЮЌГжИпЖЫЭЈаХЗўЮёЫљашЕФДѓСПДцДЂЦїДјПэЁЃДцДЂЦїЯЕЭГОпгагУгкВЂааЗУЮЪЕФ Flash/ROM ЭтВПДцДЂЦїЖЫПкКЭ DRAM ЖЫПкЃЌвдТњзуИпДјПэЁЃ DRAM ПижЦЦїжЇГж LPDDR1ЃЈвЦЖЏ DDRЃЉЁЂDDR2 Лђ LPDDR2ЁЃ

Flash/ROM ЖЫПкжЇГж NAND FlashЁЂNOR-FlashЁЂOneNANDЁЂSRAM КЭ ROM РраЭЕФЭтВПДцДЂЦїЁЃ

ЮЊСЫНЕЕЭЯЕЭГзмГЩБОВЂдіЧПећЬхЙІФмЃЌ

S5PV210АќРЈаэЖргВМўЭтЩшЃЌР§Шч TFT 24 ЮЛецВЪЩЋ LCD ПижЦЦїЁЂЩуЯёЭЗНгПкЁЂMIPI DSIЁЂCSI-2ЁЂЕчдДЙмРэЯЕЭГЙмРэЦїЁЂATA НгПкЁЂЫФИі UARTЁЂ 24 ЭЈЕР DMAЁЂЮхИіЖЈЪБЦїЁЂЭЈгУ I/O ЖЫПкЁЂШ§Иі I2SЁЂS/PDIFЁЂШ§ИіЃЈЭЈгУЃЉIIC-BUS НгПкЁЂСНИі HS-SPIЁЂUSB Host 2.0ЁЂИпЫйдЫааЕФ USB 2.0 OTG (480Mbps) ЁЂЫФИі SD жїЛњКЭИпЫйЖрУНЬхПЈНгПкЃЌвдМАЫФИігУгкЪБжгЩњГЩЕФ PLLЁЃ

Дјга MCP ЕФАќЩЯАќ (POP) бЁЯюПЩгУгкаЁГпДчгІгУЁЃ

-

1.2

S5PV210ПђЭМ

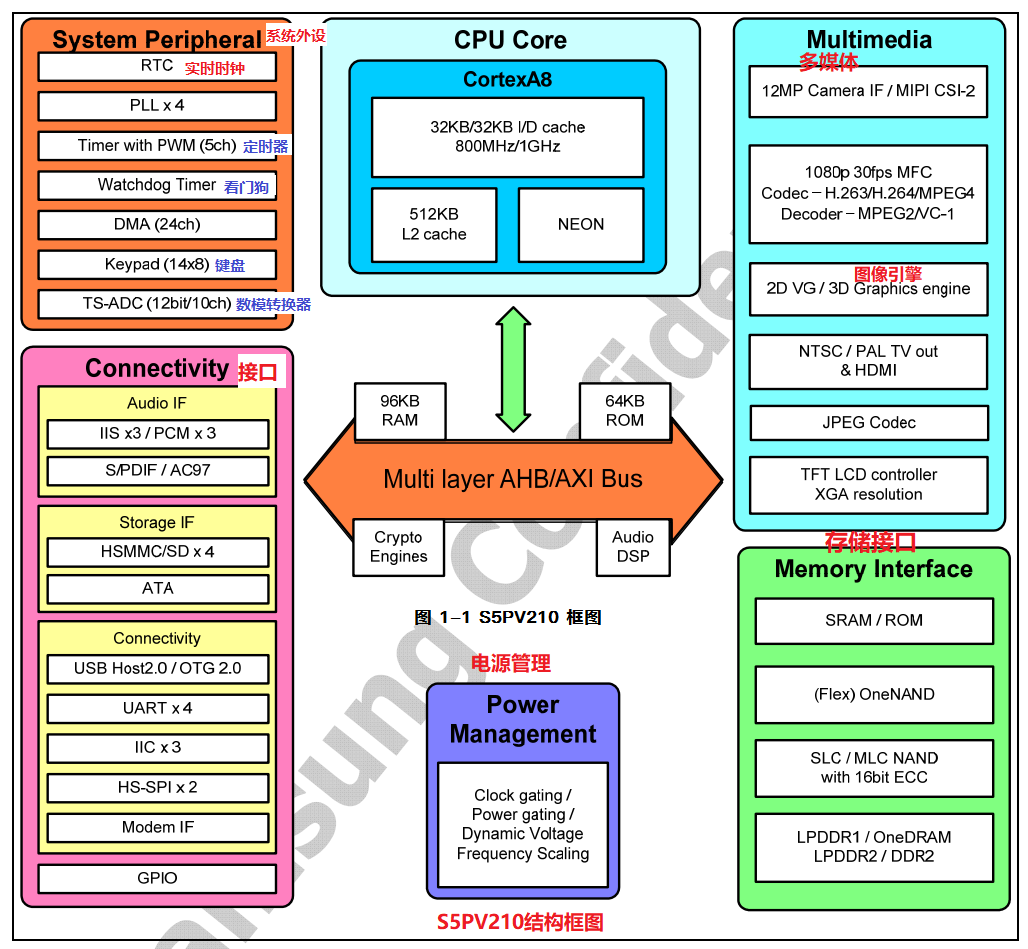

S5PV210ЕФЭъећПђЭМШчЭМ 1-1 ЫљЪОЁЃ

-

1.3

S5PV210ЕФжївЊЬиадS5PV210ЕФжївЊЬиадАќРЈЃК

? Дјга NEON ЕФЛљгк ARM CortexTM-A8 ЕФ CPU згЯЕЭГ

? 32/ 32 KB I/D ЛКДцЃЌ512 KB L2 ЛКДц

? ЙЄзїЦЕТЪИпДя 800 MHz Лђ 1 GHz

? 64 ЮЛЖрВузмЯпМмЙЙ

? ARM CortexTM-A8 ЕФ MSYS гђЁЂ3D в§ЧцЁЂЖрИёЪНБрНтТыЦїКЭжаЖЯПижЦЦї

? ЙЄзїЦЕТЪИпДя 200 MHz

? DSYS гђжївЊгУгк Display IPЃЈШч LCD ПижЦЦїЁЂCamera interface КЭ TVoutЃЉКЭ MDMA

? ЙЄзїЦЕТЪИпДя 166 MHz

? PSYS гђжївЊгУгкЦфЫћЯЕЭГзщМўЃЌР§ШчЯЕЭГЭтЩшЁЂЭтВПДцДЂЦїНгПкЁЂЭтЮЇ DMAЁЂСЌНг IP КЭвєЦЕНгПкЁЃ

? ЙЄзїЦЕТЪИпДя 133 MHz

? гУгкЕЭЙІКФвєЦЕВЅЗХЕФвєЦЕгђ

? вЦЖЏгІгУЕФИпМЖЕчдДЙмРэ

? 64 KB ROM гУгкАВШЋЦєЖЏКЭ 96 KB RAM гУгкАВШЋЙІФм

? 8 ЮЛ ITU 601/656 ЯрЛњНгПкжЇГжЫЎЦНГпДчИпДя 4224 ЯёЫиЕФЫѕЗХКЭ 8192 ЯёЫиЕФЮДЫѕЗХЗжБцТЪ

? ЖрИёЪНБрНтТыЦїЬсЙЉИпДя 1080p@30fps ЕФ MPEG-4/H.263/H.264 БрТыКЭНтТывдМАИпДя 1080p@30 fps ЕФ MPEG-2/VC1 ЪгЦЕНтТы

? ОпгаПЩБрГЬзХЩЋЦїЕФ 3D ЭМаЮМгЫйИпДя 2000 ЭђИіШ§НЧаЮ/УыКЭ 1000 ИіАйЭђЯёЫи/Уы

? 2D ЭМаЮМгЫйИпДя 160Mpixels/s

? 1/ 2/ 4/ 8 bpp Palletized Лђ 8/ 16/ 24 bpp Non-Palletized ВЪЩЋ TFT НЈвщИпДя XGA ЗжБцТЪ

? ЕчЪгЪфГіКЭ HDMI НгПкжЇГж NTSC КЭ PAL ФЃЪНЃЌДјгаЭМЯёдіЧПЦї

? MIPI-DSI КЭ MIPI-CSI НгПкжЇГж

? 1 Иі AC-97 вєЦЕБрНтТыЦїНгПкКЭ 3 ЭЈЕР PCM ДЎаавєЦЕНгПк

? Ш§Иі 24 ЮЛ I2S НгПкжЇГж

? 1 Иі TX only S/PDIF НгПкжЇГжЪ§зжвєЦЕ

? Ш§Иі I2C НгПкжЇГж

? СНИі SPI жЇГж

? ЫФИі UART жЇГжШ§ИігУгкРЖбР 2.0 ЕФ Mbps ЖЫПк

? ЦЌЩЯ USB 2.0 OTG жЇГжИпЫйЃЈ480 MbpsЃЌЦЌЩЯЪеЗЂЦїЃЉ

? ЦЌЩЯ USB 2.0 жїЛњжЇГж

? вьВНЕїжЦНтЕїЦїНгПкжЇГж

? ЫФИі SD/ SDIO/ HS-MMC НгПкжЇГж

? ATA/ATAPI-6 БъзМНгПкжЇГж

? 24 ЭЈЕР DMA ПижЦЦїЃЈ8 ЭЈЕРгУгкФкДцЕНФкДц DMAЃЌ16 ЭЈЕРгУгкЭтЩш DMAЃЉ

? жЇГж 14x8 МќОиеѓ

? 10 ЭЈЕР 12 ЮЛЖрТЗИДгУ ADC

? ПЩХфжУЕФ GPIO

? ЪЕЪБЪБжгЁЂPLLЁЂPWM ЖЈЪБЦїКЭПДУХЙЗЖЈЪБЦї

? ЯЕЭГЖЈЪБЦїжЇГждкЕєЕчФЃЪНЃЈЫЏУпФЃЪНГ§ЭтЃЉЯТЬсЙЉзМШЗЕФЕЮД№ЪБМф

? ФкДцзгЯЕЭГ

? Дјга x8 Лђ x16 Ъ§ОнзмЯпЕФвьВН SRAM/ ROM/ NOR НгПк

? NAND НгПкгы x8 Ъ§ОнзмЯп

? Дј x16 Ъ§ОнзмЯпЕФИДгУ/НтИДгУ OneNAND НгПк

? LPDDR1 НгПкгы x16 Лђ x32 Ъ§ОнзмЯпЃЈИпДя 400 Mbps/pin DDRЃЉ

? DDR2 НгПкгы x16 Лђ x32 Ъ§ОнзмЯпЃЈИпДя 400 Mbps/pin DDRЃЉ

? LPDDR2 НгПкЃЈИпДя 400 Mbps/pin DDRЃЉ -

1.3.1 ЮЂДІРэЦї

- ИУЮЂДІРэЦїЕФжївЊЬиадАќРЈЃК

? ARM CortexTM-A8 ДІРэЦїЪЧЕквЛПюЛљгкARMv7 МмЙЙЕФгІгУДІРэЦїЁЃ

? ARM CortexTM-A8 ДІРэЦїФмЙЛНЋЫйЖШРЉеЙЕН 1 GHzЃЌТњзуЙІКФгХЛЏЕФвЦЖЏЩшБИЕФвЊЧѓЃЌетаЉЩшБИвЊЧѓвдЕЭгк 300mW ЕФЫйЖШдЫааЃЛадФмгХЛЏЕФЯћЗбРргІгУГЬађашвЊ 2000 Dhrystone MIPSЁЃ

? жЇГжЪзИіВЩгУ ARM ММЪѕЕФГЌБъСПДІРэЦїЃЌгУгкдіЧПДњТыУмЖШКЭадФмЃЌNEONTM ММЪѕгУгкЖрУНЬхКЭаХКХДІРэЃЌвдМА Jazelle® RCT ММЪѕгУгкдіЧПДњТыУмЖШКЭадФмЁЃ

Java КЭЦфЫћзжНкТыгябдЕФЬсЧАКЭМДЪББрвыЁЃ

? ARM CortexTM-A8 ЕФЦфЫћЬиадАќРЈЃК

? Thumb-2 ММЪѕПЩЪЕЯжИќИпЕФадФмЁЂФмаЇКЭДњТыУмЖШ

? NEOTM аХКХДІРэРЉеЙ

? Jazelle RCT Java МгЫйММЪѕ

? гУгкАВШЋНЛвзКЭ DRM ЕФ TrustZone ММЪѕ

? 13 МЖжїећЪ§СїЫЎЯп

? 10 МЖ NEOTM УНЬхЙмЕР

? ЪЙгУБъзМБрвы RAM ЕФМЏГЩ L2 ЛКДц

? еыЖдадФмКЭЙІКФгХЛЏЕФ L1 ЛКДц

- ИУЮЂДІРэЦїЕФжївЊЬиадАќРЈЃК

-

1.3.2 ФкДцзгЯЕЭГ

ФкДцзгЯЕЭГЕФжївЊЬиадАќРЈЃК

? ИпДјПэФкДцОиеѓзгЯЕЭГ

? СНИіЖРСЂЕФЭтВПДцДЂЦїЖЫПкЃЈ1 x16 ОВЬЌЛьКЯДцДЂЦїЖЫПкКЭ 2 x32 DRAM ЖЫПкЃЉ

? ОиеѓМмЙЙЭЈЙ§ЭЌЪБЗУЮЪФмСІдіМгСЫећЬхДјПэ

? SR