值为16‘h0;其他协议根据具体情况修改;

end

else begin

lfsr_q <= crc_en ? lfsr_c : lfsr_q;//此处crc_en设为0,只计算一次即输出CRC校验结果,否则会持续不断进行运算

end

end

endmodule

编写testbench文件对该模块进行仿真:

module crc_simul;

reg [63:0] data_in;

reg crc_en;

reg reset;

reg clk;

wire [15:0] crc_out;

crc uut(

.data_in(data_in),

.crc_en(crc_en),

.crc_out(crc_out),

.reset(reset),

.clk(clk)

);

initial begin

data_in = 64'd0;

crc_en = 1'b0;

reset=1'b0;

clk = 1'b0;

#9;

reset=1'b1;

#200;

data_in = {8'hFF,8'hFF,8'hAA,8'h55,8'h00,8'h01,16'h13EC};//结果应为3DC3;

#500;

data_in = {8'hFF,8'hFF,8'hAA,8'h55,8'h00,8'h01,16'h01F4};//结果应为CBEB;

end

always #1 clk = ~clk;

endmodule

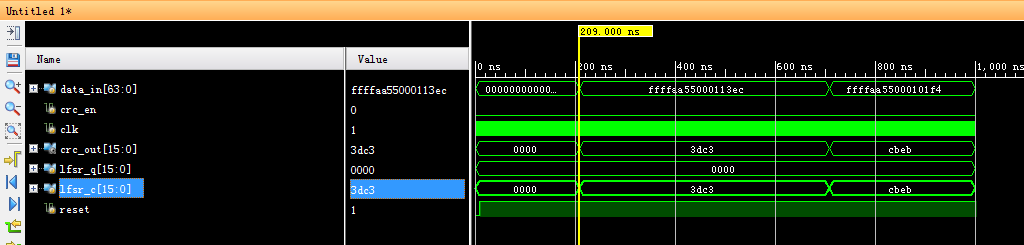

仿真结果如下

可以验证,仿真结果正确,在实际应用中也可以正确运行;