4'd1)? 1'b1:1'b0;

74 assign csh2=(encode_adder[7:4] == 4'd2)? 1'b1:1'b0;

75 assign csh3=(encode_adder[7:4] == 4'd3)? 1'b1:1'b0;

76 endmodule

View Code

系数池ROM就是一个简单的单端口ROM,其结构如下图所示。

图5 系数池ROM的结构示意图

其大小为256个字,但由于N为64,我只是用了系数池ROM的1/4。

六、各卷积节求和电路的设计

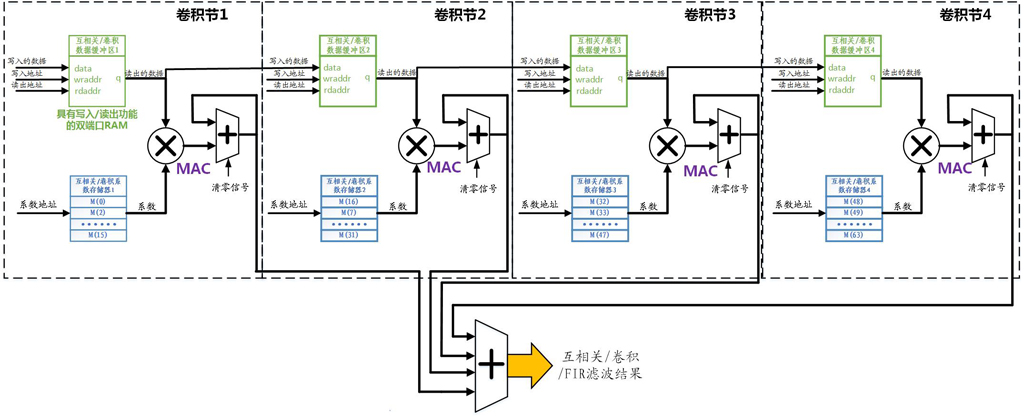

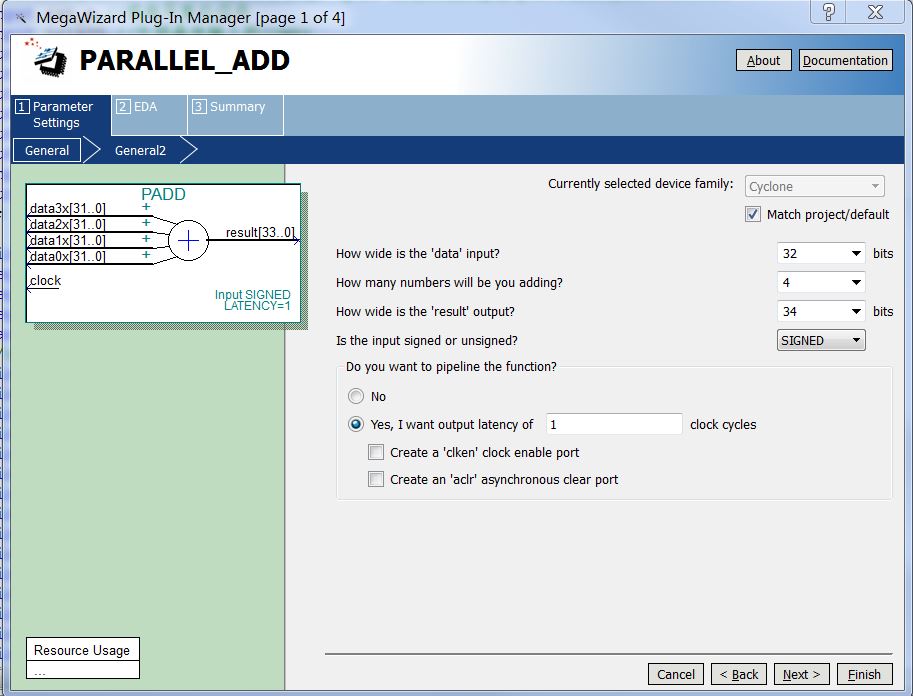

如图1所示,还需要对L个卷积节的结果求和,才能得到半并行式互相关/卷积/FIR滤波器的最终结果。使用Quartus-II的MegaWizard调用PARALLEL_ADD这个IP,能实现最终求和。其结构如下图所示。

图6 并行加法器结构示意图

关于回波检测中功率(平方)计算、历史数据积分等算法在FPGA中的实际实现,请关注后续博文【目标反射回波检测算法及其FPGA实现之三:平方、积分电路及算法的顶层实现】。

关于目标回波检测算法原理和设计论证过程,请参看本人的上一篇博文【 目标反射回波检测算法及其FPGA实现 之一:算法概述 】。