Notepad++是一款精致小巧的编辑器,自带Verilog语法识别功能,插件也挺好用的。尤其是利用插件实现代码片段,大大节省我们写Verilog的时间。此外少有人知道的,可以利用某款插件实现在Notepad++界面中编译Verilog的功能。下面就来说说这几个功能要如何设置。

版本:Notepad++ 7.6.6 ,32位

//========================================================================

//== 安装与Verilog设置

//========================================================================

1.点击.exe安装Notepad++

2.打开Notepad++,点击“语言(L)”选择Verilog,点击编码(N)选UTF-8

3.点击视图(L)勾选“自动换行”

4.点击设置(T)---首选项

1)常用---文件列表面板---勾选“显示”

2)编辑---勾选“启用滚动超过最后一行”

3)新建---编码---选择UTF-8(无BOM),勾选“应用于打开ANSI文件”

4)最近文件记录---勾选“不要在启动时检查”

5)语言---制表符宽度设置为“4”,勾选“替换成空格”

6)备份---不勾选“记住最后打开的文件”,备份勾选“禁用”,这样就不生成讨厌的备份文件了

7)自动完成---勾选( 、 [ 、 " ,千万别勾选 ' 不然写1'b1时就麻烦了

8)其他---勾选“自动缩进”,不勾选“启用Notepad++自动更新”

5.点击设置(L)---语言格式设置---字体选择Consolas,勾选“使用全局字体”---保存并退出,该字体为等宽字体,中英文符号区别明显,适合编程。

6.点击设置(L)---语言格式设置---这里可以选择主题,个人推荐Monokai和Obsidan,如果主题中还有不满意的地方也可以进一步微调,例如选中语言:Global Styles,这是全局的风格,选择Selected text colour是改变选中文本的颜色,选择Smart HighLighting是改变选中单词后的高亮颜色,这两个要改的话都是改背景色。选中语言:Verilog,这是专门针对Verilog的风格,一般改前景色就行。即使打开了这个设置页面,Notepad++也是可以继续编辑的,所以可以一个个选项去试,可以实时看到效果,试错了点击取消即可恢复。

//========================================================================

//== 插件:代码片段

//========================================================================

1.打开Notepad++,点击插件(P)---插件管理---可用---勾选“Finger Text”---点击安装,点是。Notepad++会自动退出,过大概20秒自动打

开,这就安装好了。

2.点击插件(P),看到已经出现了Finger Text,点击里面的Toggle on/off snippetDock,界面右边出现了工作栏,点击Open Snippet Editor

3.代码片段的设置很简单,分三栏:

第一栏:唤醒字,设置成功后打出唤醒字,按Tab键即可出现代码片段。

第二栏:使用范围,默认是全局,可以不改,也可以改成:Lang:Verilog

第三栏:代码片段,自己的代码片段填上去,末尾写上结束符<End>即可。符号$[0[]0]是设置生成该代码片段时最后鼠标的停留位置;符号$[![]!]是设置按Tab键时的跳转位置;如果在该代码片段多处出现$[![a]!]符号,那么在该处写代码时,所有含该符号的位置,代码是一起被写上的。

设置好后保存即可。

4.点击工作栏的“Export All”可以保存自己设置好的所有代码片段文件

5.点击工作栏的“Import ftd File”可以导入代码片段文件。

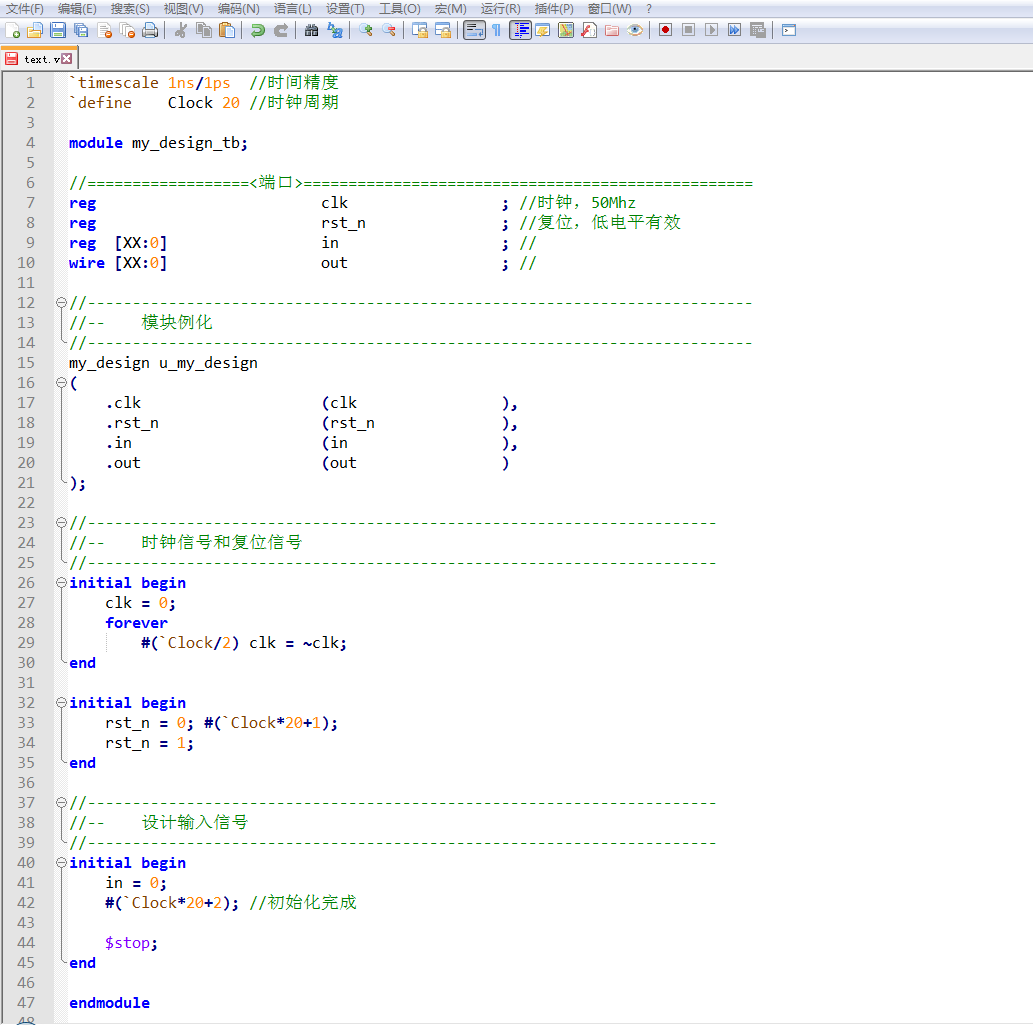

如图是我用该插件写好的代码片段,唤醒字设置为 tb ,敲下tb按tab键即自动出现如下的仿真模板,真的非常方便。将常用的Verilog代码片段写好,以后写代码就快多了!

//========================================================================

//== 插件:编译Verilog

//========================================================================

1.安装插件:NppExec

2.按F6,输入:cmd /k cd "$(CURRENT_DIRECTORY)" & vlog.exe "$(FULL_CURRENT_PATH)" & ECHO. & EXIT

保存,命名为:Run Verilog

3.用Modelsim新建一个工程,添加文件进行编译。退出Modelsim,找到刚刚那个工程目录的文件夹:work,将其复制到你的Notepad++的安装目录下。

4.Notepad++打开任意一个.v文件(含中文路径也可以),按F6,点击OK(也可按Enter键),看到界面下方弹出Console控制台,显示出了本该在Modelsim中的编译结果。

5.建议勾选:插件---NppExec---No internal messages,这可以让编译窗口的信息更简洁。

6.建议勾选:插件---NppExec---Save all files on execute,这样按F6编译时,插件会先自动保存再编译。如果不勾选则需要先手动保存代码再编译。

如下所示在代码的第14行,逗号误写成了分号,按下F6键进行编译,Console控制台就显示出了这条语法错误信息。以后Verilog找语法bug不需要再傻乎乎的打开Quartus或Modelsim来建工程了,Notepad++快人一步!