在这一小节中,我们详细分析BJT的共基组态电路。在BJT的共基组态中,“输入端口”和“输出端口”共用BJT的基极端子(故称为“共基”),形成一个双端口网络,如下图所示:

图 3-3.01

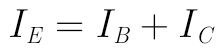

无论是npn型还是pnp型,下式总是成立的,这是我们后面分析的基础公式:

在后面的分析中,我们都将以npn型晶体管为例进行分析;pnp的分析方法其实是一样的,只是电流方向相反而已。

在上面图3-3.01的双端口网络中,我们有四个参数要研究(VBE, IE, VCB , IC),理论上讲,必须固定其中一组电压与电流,才能对剩下的一组电压和电流画伏安特性曲线。但是由于BJT有一个端子被输入输出端口共用,所以实际上只有2个自变量。我们以下图举例:

图 3-3.02

上图中,只有VEE和VCC是自变量,IE和IC都是应变量。比如,我们只要固定了VCC,就可以通过变化VEE,来研究IE-VEE之间的伏安关系。换句话说,某个端口的电流完全由输入和输出两个端口的电压来控制(这种控制就是BJT的基本作用)。此时,IC的值也完全由VEE和VCC决定,我们在研究IE-VEE伏安关系时,可以不关心IC的值。

再比如,我们也可以调整VEE使IE为固定值,然后通过变化VCC,来研究IC-VCC之间的伏安关系,如下图所示:

图 3-3.03

此时,我们调整VEE的主要目的是为了使IE固定,VEE完全可由IE确定,我们在研究IC-VCC伏安关系时,可以不关心VEE的值。

1. 输入特性

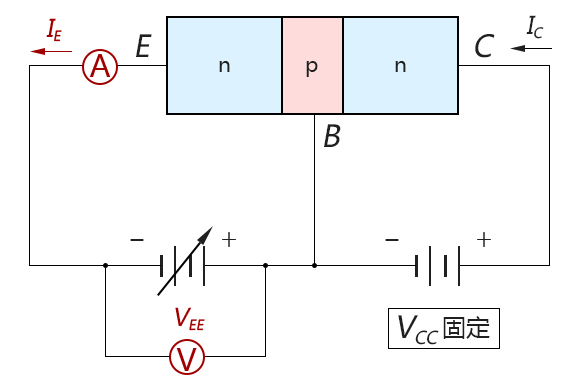

共基组态型电路的输入特性(input characteristics)是指:在一定的输出电压VCB下,输入电压和输入电流之间的关系(即:VBE-IE伏安关系)。

共基组态电路的输入特性伏安特性图如下图所示:

图 3-3.04

从上图中我们可以看到,VBE-IE的伏安曲线与二极管特性曲线很相似。而且可以看到,不同的集电结偏置电压VCB对于输入特性的影响非常小,几乎可以忽略。甚至我们可以将它像二极管一样作分段近似,如下图所示:

图 3-3.05

上图可以理解为:当BJT在“导通”状态时,不管射极电流IE如何变化,VBE的值固定在0.7V左右,因此IE的大小实际由电路的其他部分控制。这个结论不只在共基组态成立,在BJT的其他组态中也是成立的。

2. 输出特性

共基组态型电路的输出特性(output characteristics)是指:在一定的输入电流IE下,输出电流与输出电压的关系(即:VCB-IC伏安关系)。

共基组态电路的输出特性伏安特性图如下图所示:

图 3-3.06

上图中我们可以看到,输出伏安特性曲线图分为3个区域,分别是:放大区、截止区、饱和区,下面我们分别进行详细描述:

(1) 放大区

放大区(active region)是图中绿色部分,占据曲线图的大部分面积。当共基组态电路的:发射结正偏、集电结反偏时(就是我们前面分析过的最常用的偏置组合),伏安曲线就处于放大区。

对于放大区范围内的伏安特性曲线,我们可以看出以下2个特性:

① 在放大区范围内伏安曲线看上去几乎水平,这说明VCB对集电极电流IC几乎没有什么影响。

② 对于每一个特定发射极电流IE,集电极电流IC几乎就等于IE,即:IE ≈ IC

(2) 截止区

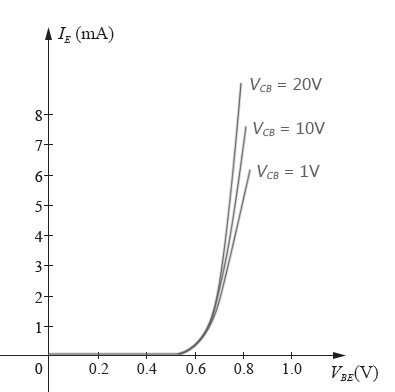

截止区(cutoff region)是图中红色区域部分。当共基组态电路的:集电结反偏、发射结偏置电压为0或反偏时,发射极电流IE≤0, 伏安曲线就处于截止区。

其偏置情况用下图进行说明:

图 3-3.07

当发射结偏置电压为0(即:发射结开路)时,如上左图所示,IE=0。当发射结反偏时,如上右图所示,此时发射结中只有微弱的反偏漏电流通过,IE<0。在这两种情况下,发射区都不再会有自由电子注入集电极,因此,集电极电流IC仅由集电结反偏电压VCB产生,数值为极其微小(纳安级)的反向漏电流ICBO,可近似认为是0。 只要不击穿,VCB的变化对ICBO几乎无影响。

因此,在IE≤0的区域,集电极电流IC都是一条数值为 0的水平直线。

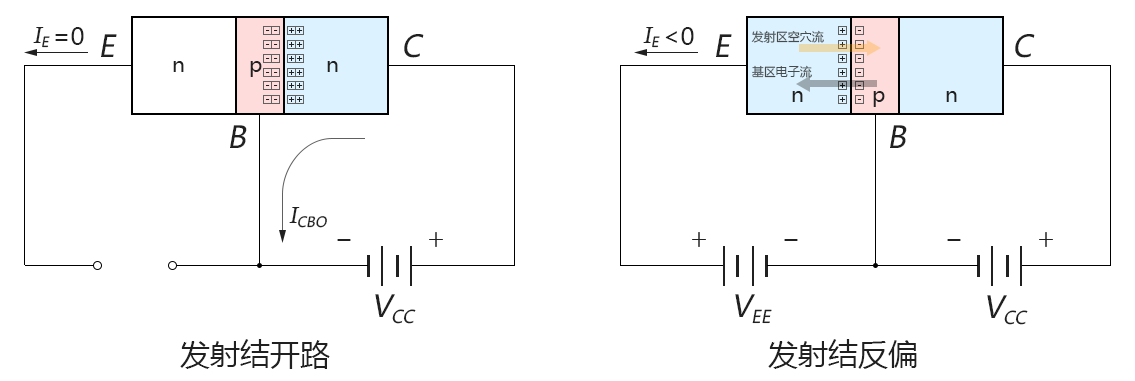

(3) 饱和区

饱和区(saturation region)是图中橙色部分。至于为什么叫作“饱和“,等我们后面讲完放大器的交流分析后,你就明白饱和是什么意思了,这里暂且不表。当共基组态电路的:发射结正偏,集电结也正偏(VCB<0)时,伏安曲线就处于饱和区。

其偏置情况用下图进行说明:

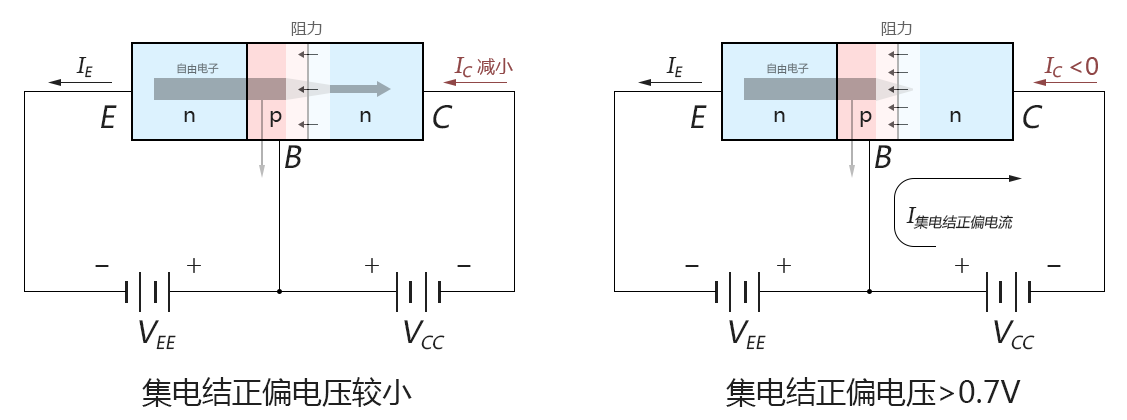

图 3-3.08

上面左图中,集电结外加的正偏电压较小,这个集电结偏置电压会产生一个偏置电场,叠加在原来集电结耗尽层自身的内置电场上(图中未画出),这个偏置电场会对发射极运动过来的自由电子产生一个阻力,使发射极冲到集电极的自由电子数量减少,在伏安曲线上表现出来就是:随着集电结正偏电压增大,IC迅速减小。

当集电结正偏电压大于某个阈值(0.7V左右)时,如上面右图所示,此时已经没有自由电子能突破这个阻力来到集电极了,发射极偏置不能再产生集电极电流IC了。此时,集电结就像一个普通二极管那样,产生正偏电流(这个电流同原来定义的IC方向相反,故为负),在伏安曲线图上表现出来就是:当VCB<-0.7V时,IC<0,并且在负方向上急速增大。

3. 参数α

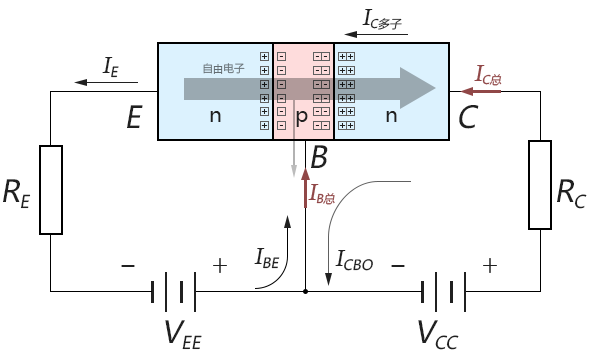

参数α(阿尔法)只能由共基组态电路来定义,我们将图3-2.05重画于下:

图 3-3.09

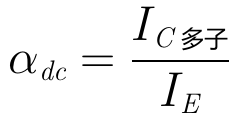

在上图中,我们定义直流参数αdc为:“IC中的多子电流分量”与IE的比值。用公式表示即为:

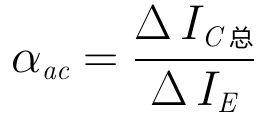

再定义交流参数αac为:当VCB不变时,“集电极电流微小相对变化”与“发射极电流的相应微小变化”的比值(注意到当VCB不变时,ICBO不变,故ΔIC多子=ΔIC总)。用公式表示即为:

交流参数α