Vivado xilinx fft9.0 使用笔记:

****注 仿真实测1024点的转换需要经过1148个时钟周期才能得到转换结果;

模块配置信号含义请参考pg109文档手册(写的贼烂会看晕),不详细说明;

一、查找fft IP核按如下几图配置可实现正确的fft转换结果:

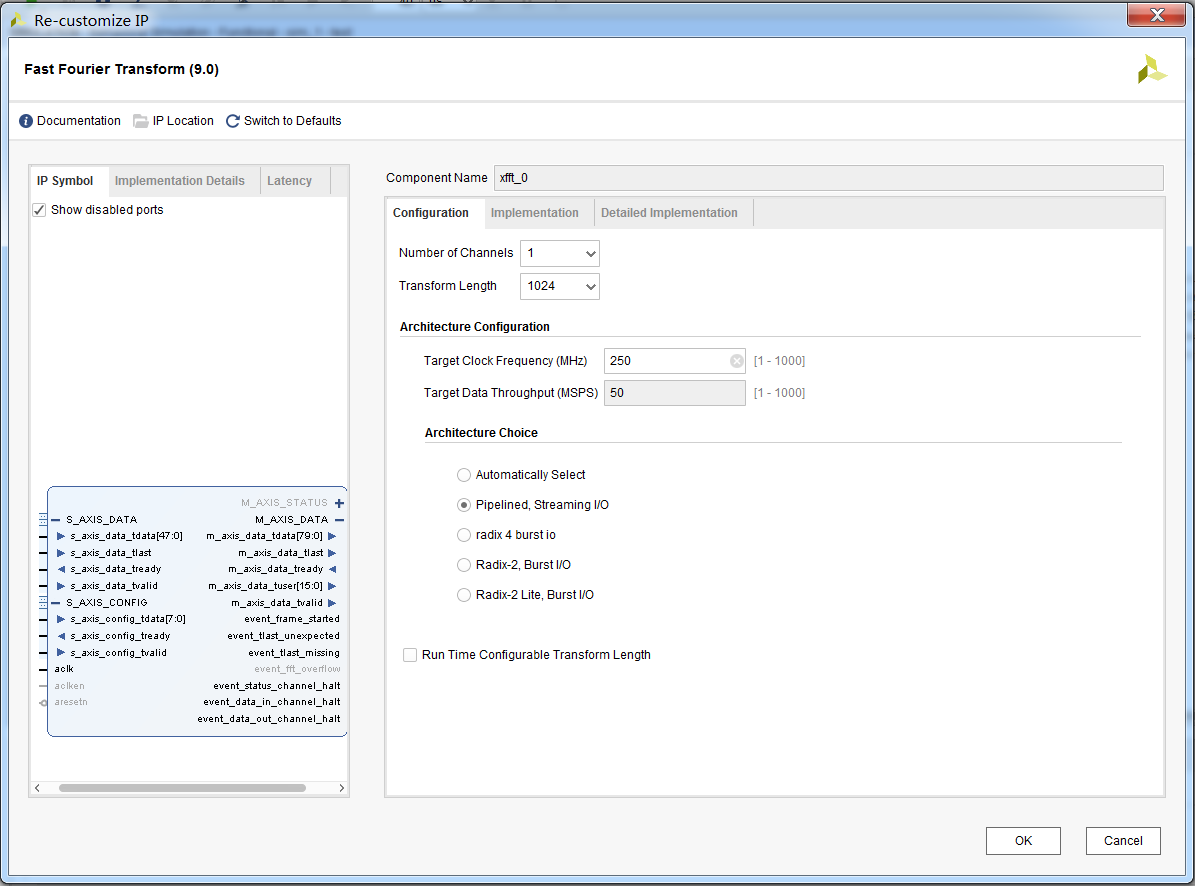

配置1个转换通道;转换数据长度是1024 points;选择流线型结构类型pipelined,streamingI/O,优点并行转换速度快,,缺点占用资源多。 如图1:

图1

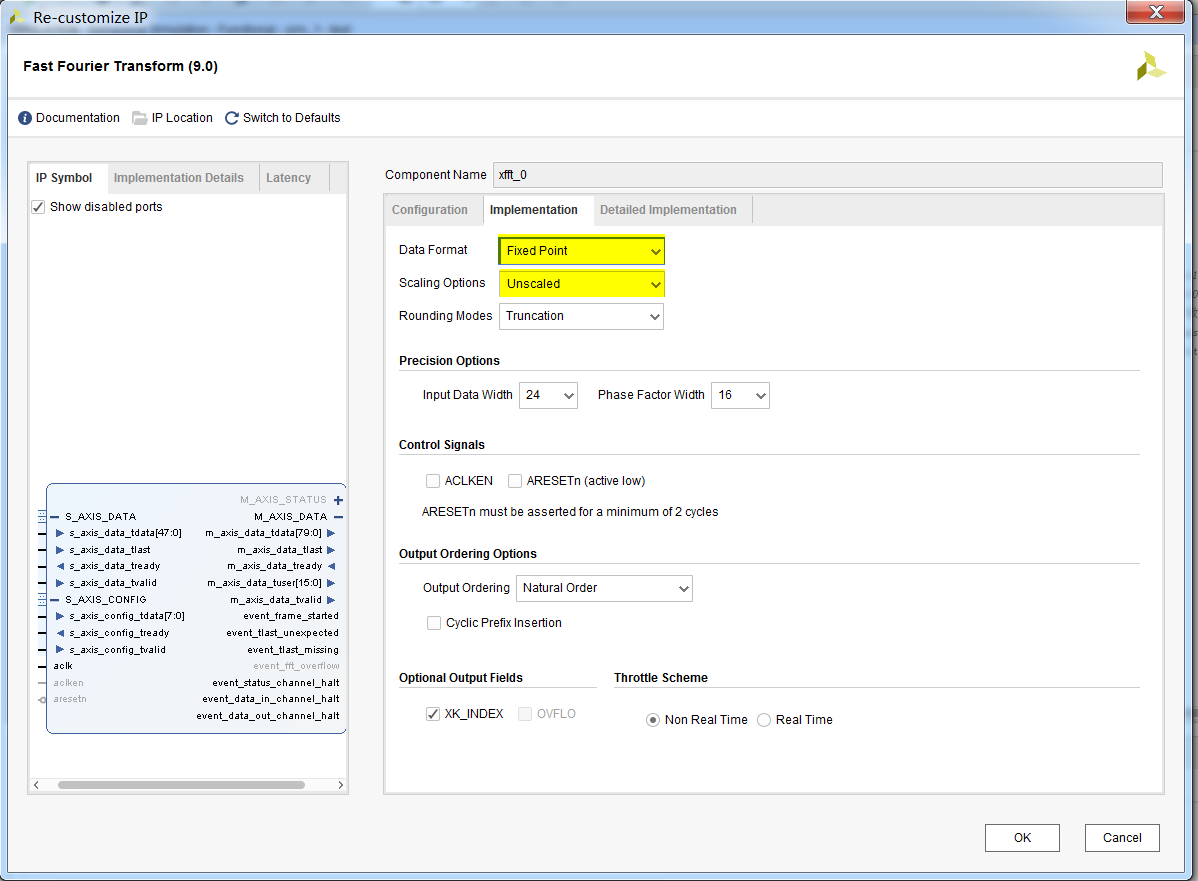

如图2,设置数据类型为定点小数;缩减因子设置成Unscaled;RoundingModes设置成Truncation;输入位宽设置24位,精度设置16;Output Ordering 设置成Natural Order;OptionalOutputFieldds勾选XK_INDEX;

图2

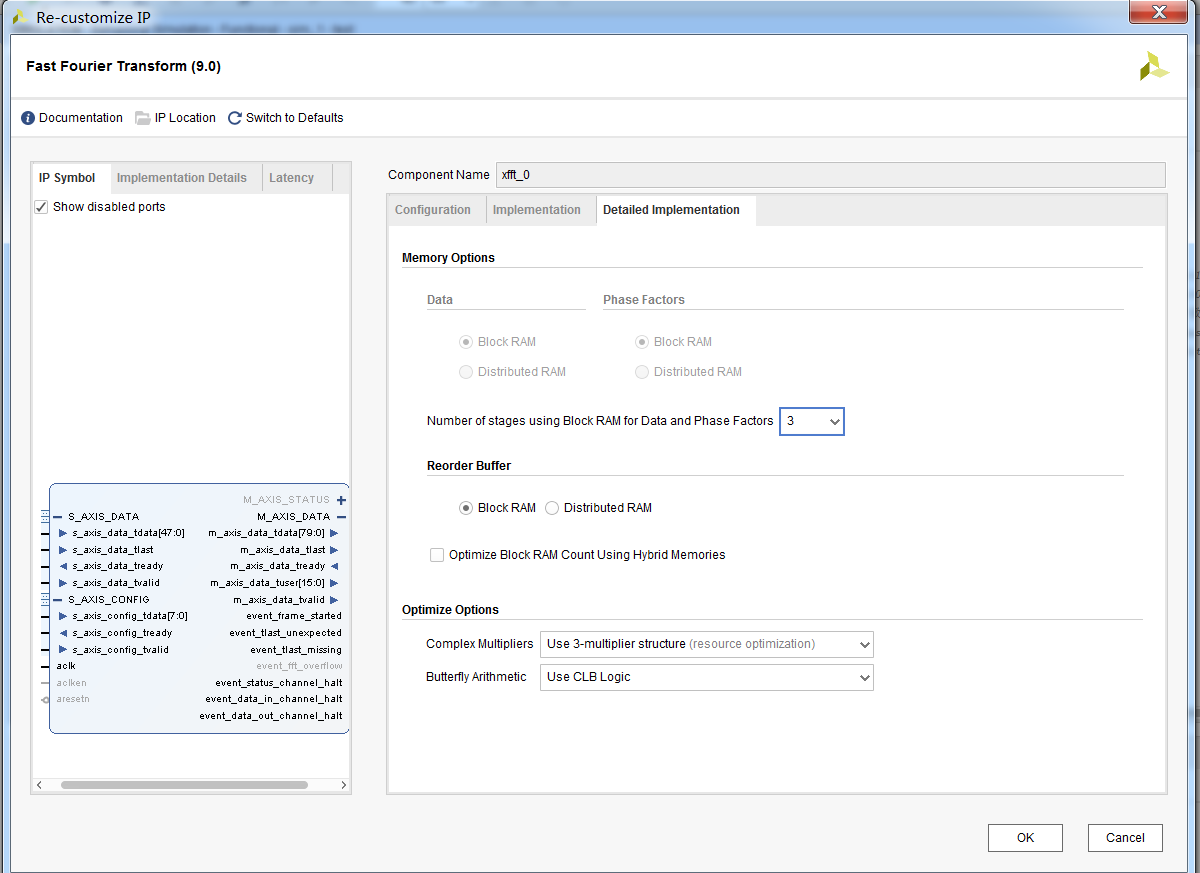

如图3 此页信息基本固定配置:

图3

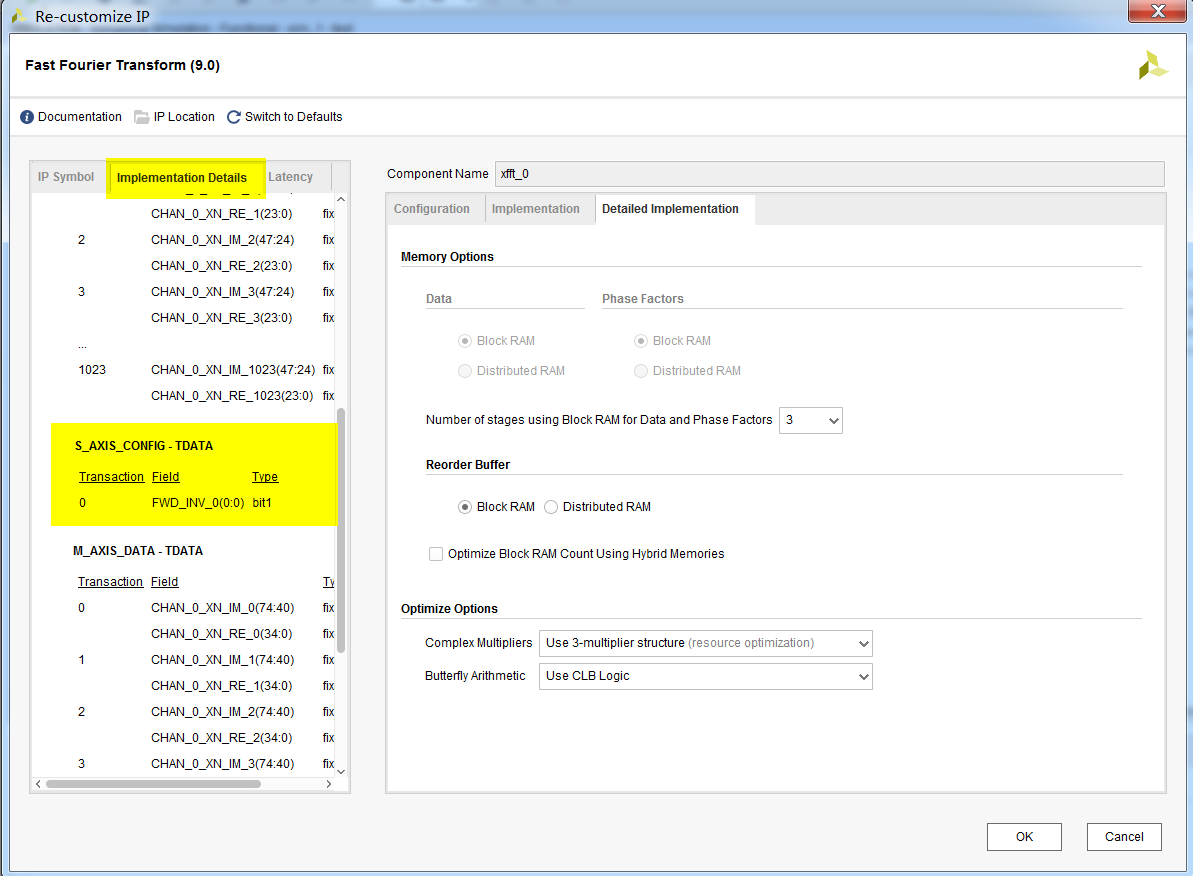

***注:注意图4中区域 有助于帮助你在编写testbenchs时对s_axis_config_tdata进行配置;

如图4 s_axis_config_tdata 只有1位配置fft的fwd/inv;

图4

Testbench代码如下:

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer: zyp

//

// Create Date: 04/21/2017 08:35:42 PM

// Design Name:

// Module Name: test

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module test();

// Inputs

reg aclk;

reg aresetn;//active low

reg s_axis_config_tvalid;

reg s_axis_data_tvalid;

reg s_axis_data_tlast;

reg m_axis_data_tready;

reg [7:0] s_axis_config_tdata;

//reg [15:0] s_axis_config_tdata;

reg [47: 0] s_axis_data_tdata;

// Outputs

wire s_axis_config_tready;

wire s_axis_data_tready;

wire m_axis_data_tvalid;

wire m_axis_data_tlast;

wire event_frame_started;

wire event_tlast_unexpected;

wire event_tlast_missing;

wire event_status_channel_halt;

wire event_data_in_channel_halt;

wire event_data_out_channel_halt;

//wire [47:0] m_axis_data_tdata;

wire [79:0] m_axis_data_tdata; //un_scaled

wire [15:0] m_axis_data_tuser;

//

//reg[23:0] XK_RE;

//reg[23:0] XK_IM;

reg[39:0] XK_RE;//config unsclaed

reg[39:0] XK_IM;//config unsclaed

reg[23:0] mem0_re[0:4095];

reg[23:0] mem1_re[0:7];

reg[23:0] mem2_re[0:7];

initial $readmemh("D:/fpga/fft1/stimulus0_24bit.dat",mem0_re);

initial $readmemh("D:/fpga/fft1/stimulus1_24bit.dat",mem1_re);

initial $readmemh("D:/fpga/fft1/stimulus2_24bit.dat",mem2_re);

reg[7:0] op_sample= 0;

reg op_sample_first = 1;

reg[7:0] ip_frame=0;

reg[7:0] op_frame=0;

integer i;

// generate clk

always #5 aclk =! aclk;

xfft_0 xfft_m0 (

.aclk(aclk), // input wire aclk

// .aresetn(aresetn),

.s_axis_config_tdata(s_axis_config_tdata), // input wire [7 : 0] s_axis_config_tdata

.s_axis_config_tvalid(s_axis_config_tvalid), &