绪论

本文将介绍一个完全用Verilog HDL手写的AMBA片上系统,

项目的主题是设计一个基于AMBA总线的流水灯控制系统,

项目中所有数字逻辑电路部分都不会通过调用成熟IP核的方式来实现,而是通过Verilog进行RTL设计,

然后利用Vivado平台对RTL模型进行仿真、综合与布线,

最后在FPGA开发板上进行板级验证,

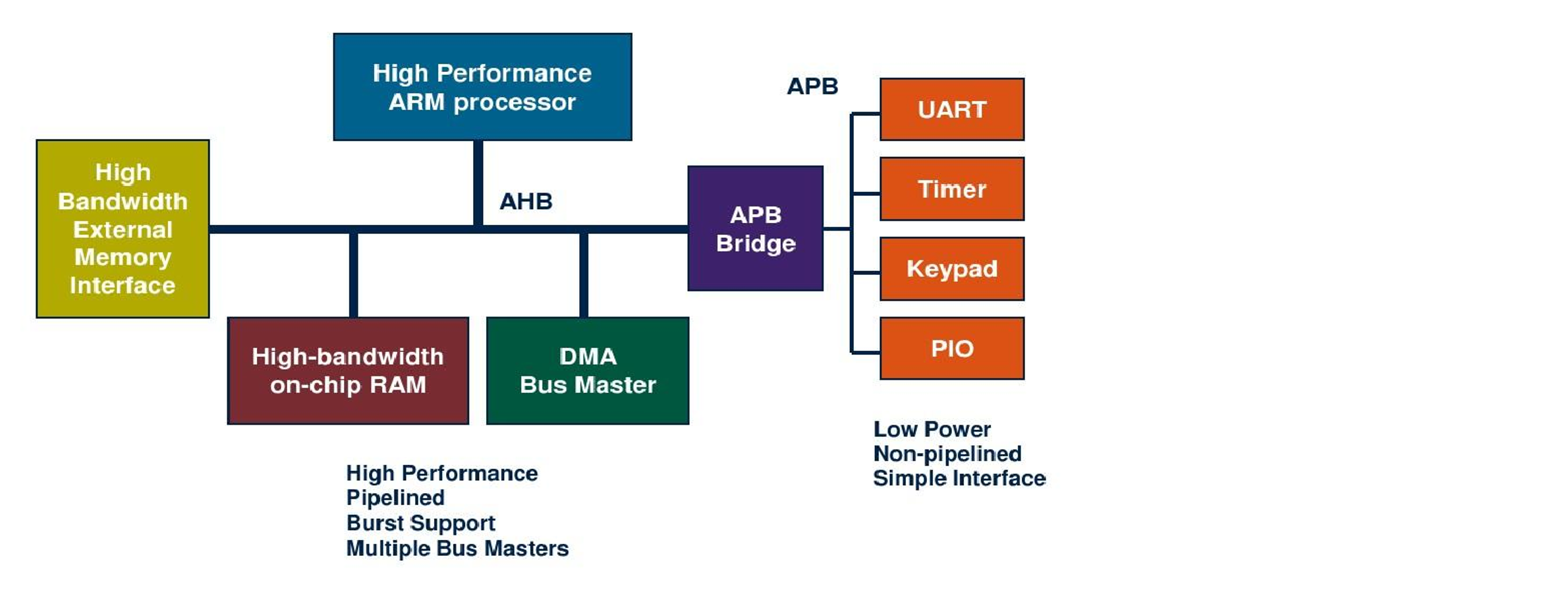

AMBA是ARM公司推出的一种总线架构,目前已非常成熟,在行业内得到广泛的应用,极具实际应用价值,

本项目涉及了AMBA架构中的AHB协议&APB协议,

系统包括AHB总线、APB总线两个部分,

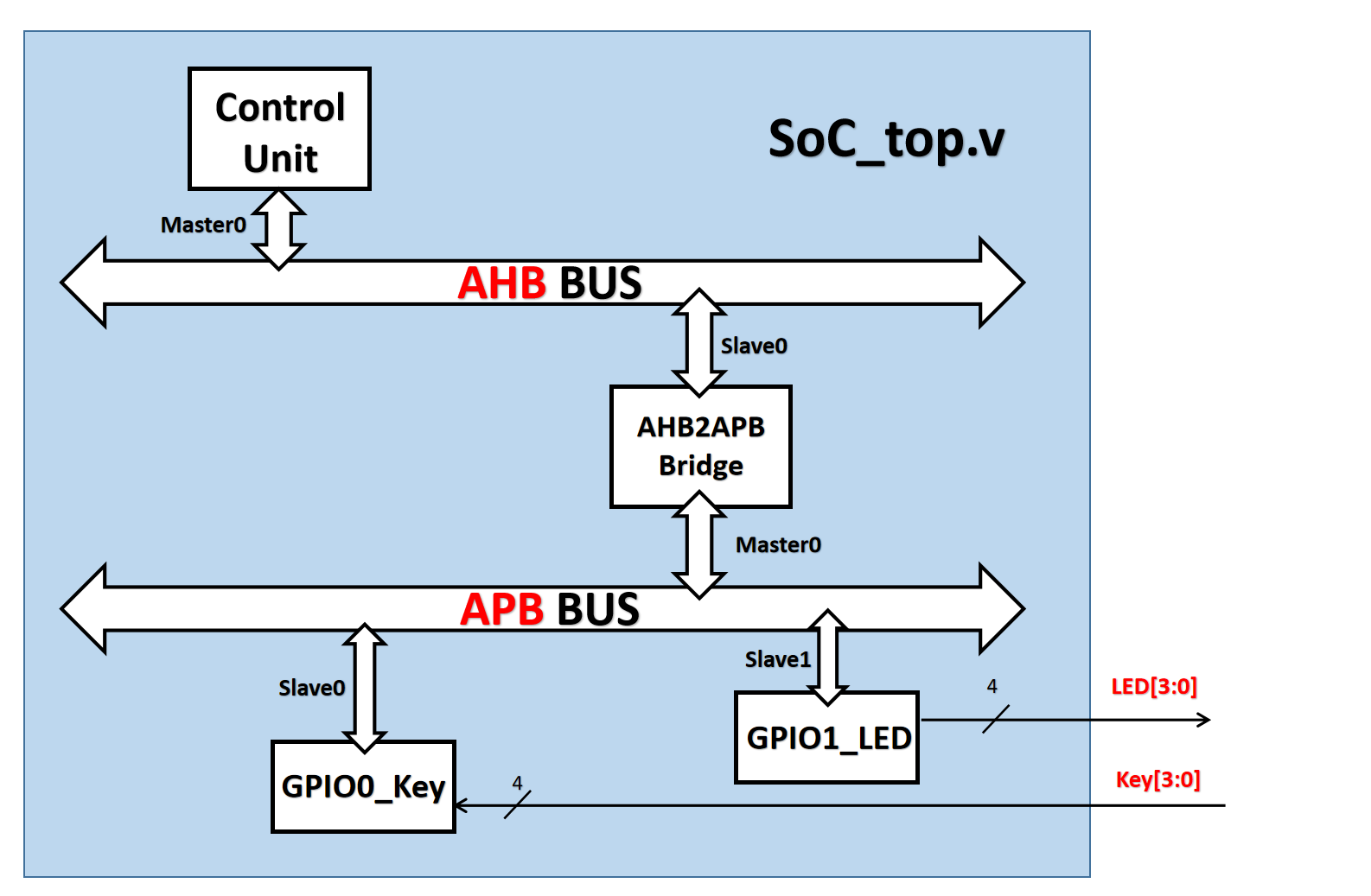

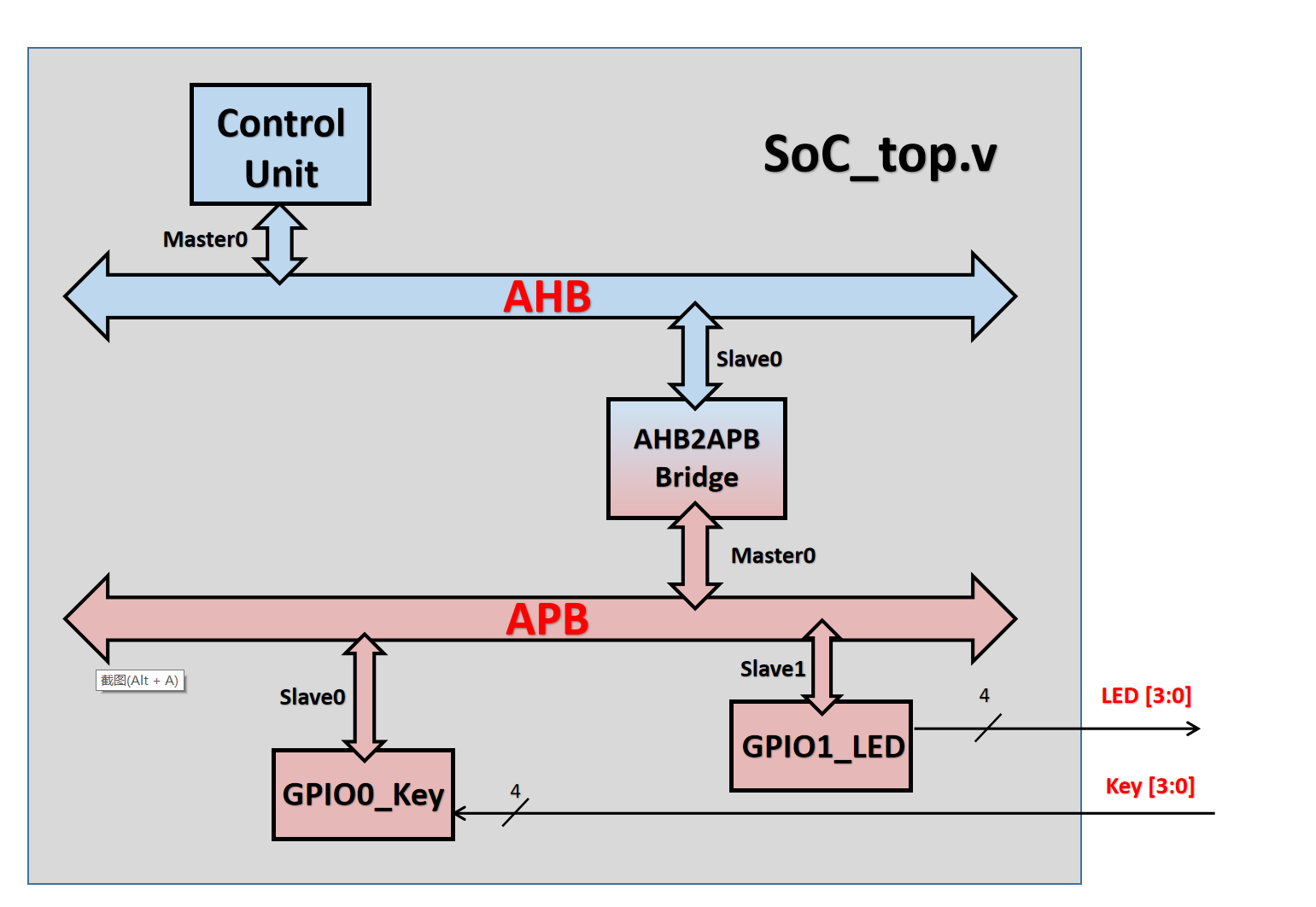

整个系统的基本架构如下图所示:

总的来说,由AHB总线上的主机――――流水灯控制单元(Control Unit),发出控制信号,

进而对APB总线上的从机GPIO模块进行配置,实现对流水灯的流动方式的控制,

本项目是一个完整的AMBA总线系统,包括总线、主机、从机以及外设,

在各章节中,将会介绍如何利用Verilog语言对以下模块进行RTL设计:

1. Control Unit模块

2. AHB2APB Bridge模块

3. GPIO模块

希望本项目能给对AMBA总线架构感兴趣的朋友们一些启发与帮助。

下面,先简要介绍一下AHB/APB总线的基本特性和数据传输时序:

AHB总线协议简介:

AHB总线,全称为Advanced High performance Bus,属于AMBA2.0规范中的一部分,

在SoC片上系统中,AHB主要用于一些高性能模块之间的连接(如CPU、DMA、DSP等),

主要的特性包括:单时钟边沿操作、支持突发传输、支持多个主控制器、可配置总线宽度(32位~128位)、支持字节、半字、字传输。

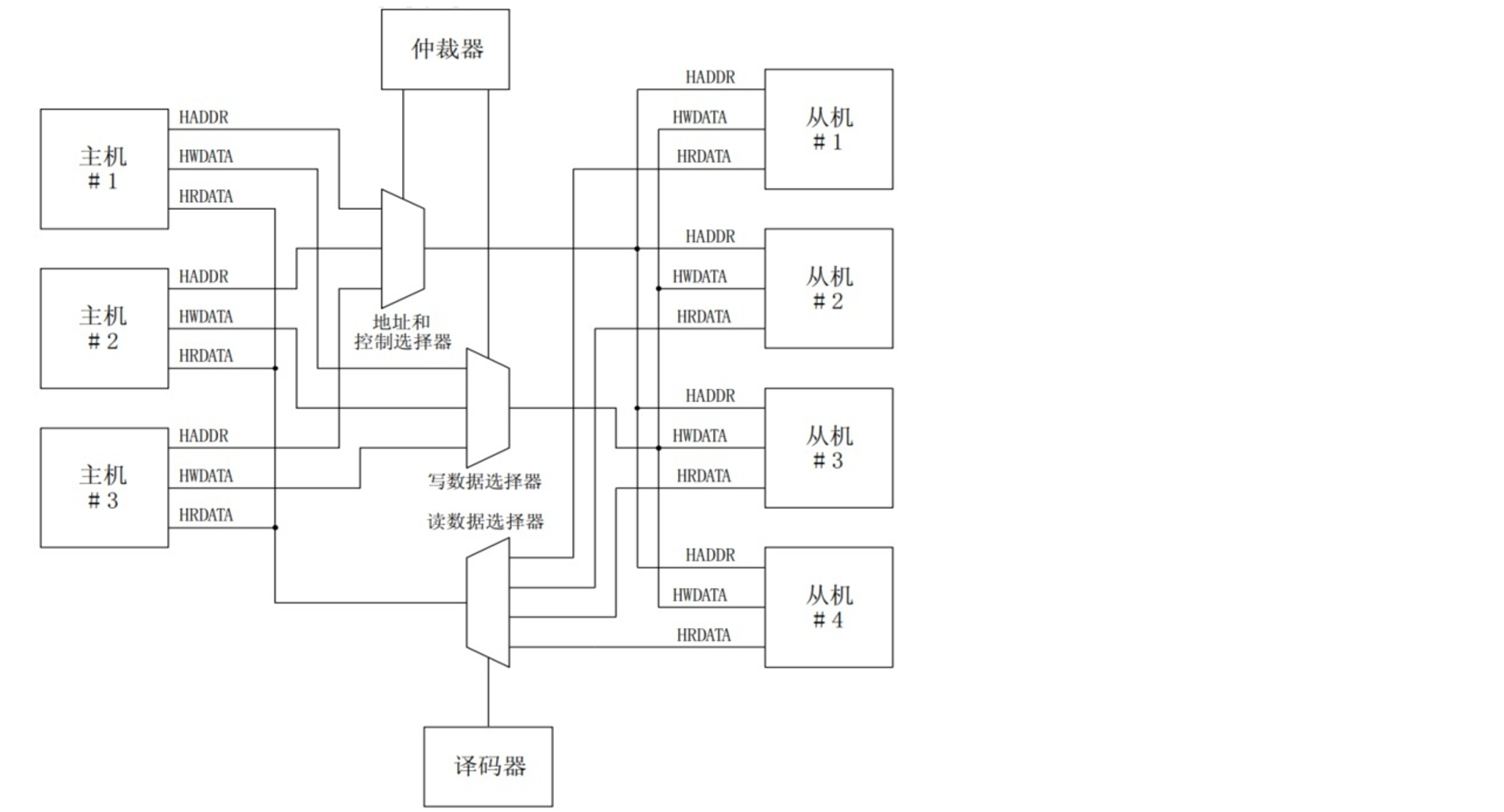

一个典型的AHB总线系统通常以下图所示的方式进行多主机多从机互联:

可以看出,Master(主机)这边的地址信号HADDR和数据信号HWDATA都是广播的,通过仲裁器arbiter给出的hselx来选择对应的从机,

而Slave(从机)这边的数据,则是通过Decoder来解码给主机这边的。

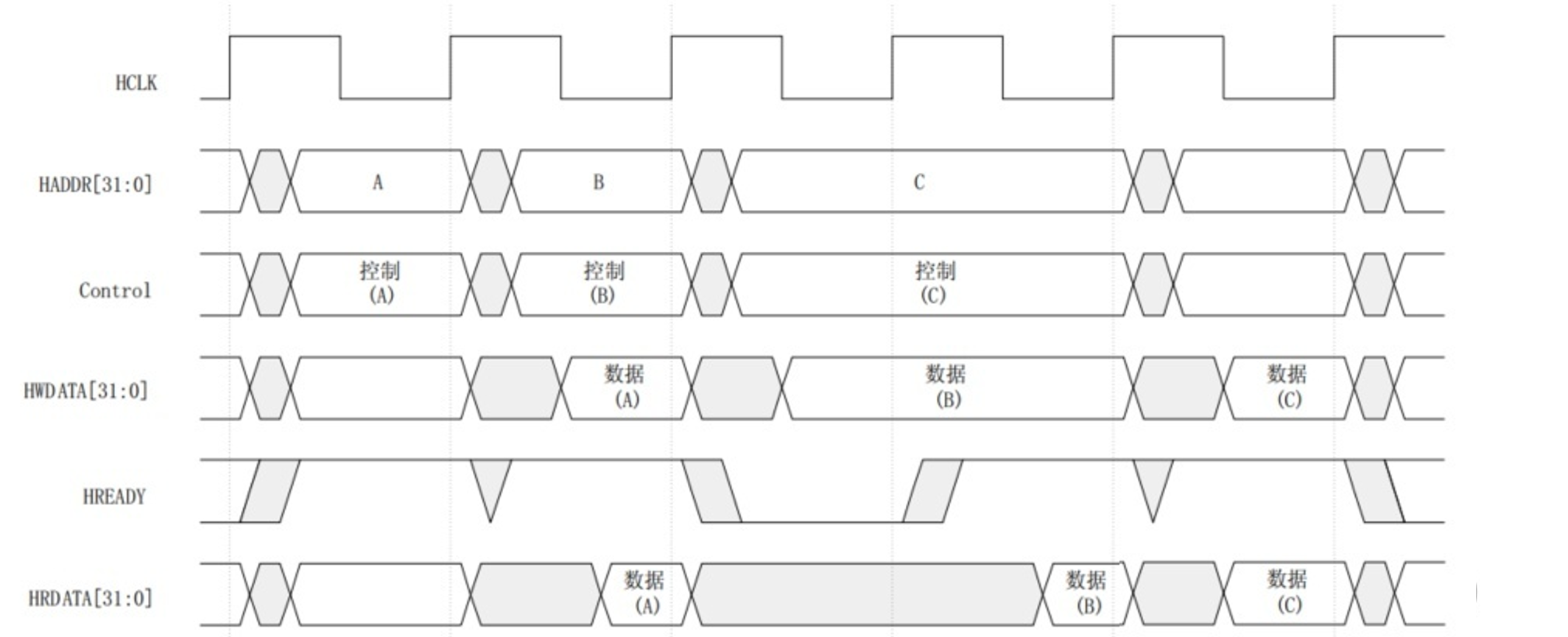

当HSELx选中对应的从设备后,就可以开始传输了,一个无等待传输的时序如下所示:

图中可以看出,AHB总线具有流水线特性,地址周期和数据周期交替进行

APB总线协议简介:

APB,全称为Advanced Peripheral Bus,主要用于低带宽的周边外设之间的连接,例如UART、1284等,

APB总线架构不像AHB支持多个Master,在APB里面唯一的Master就是APB桥。

APB总线特性包括:

-

两个时钟周期传输(非流水线,不同于AHB)

-

无需等待周期和回应信号

-

控制逻辑简单

-

只有四个控制信号

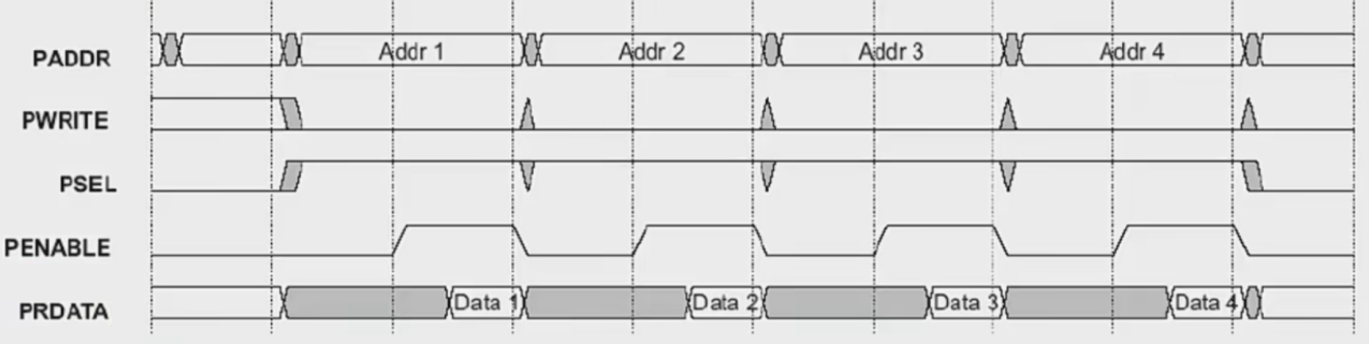

下图展示了APB总线上的一次标准的数据传输时序:

其他有关APB总线的介绍,将在下文AHB2APB Bridge模块的设计章节中涉及

1. 系统架构与功能

1.1 系统架构

本项目的系统架构框图上图所示,

其中,蓝色部分为AHB总线以及AHB上的主机从机,粉色部分则是APB总线以及APB上的主机从机,

下面介绍一下总线上各个模块的功能和定义:

-

流水灯控制单元(Contro Unit)

在AHB总线上,流水灯控制单元作为Master,

控制单元发出的AHB总线信号将经过AHB2APB Bridge,成为APB信号,

APB信号会对GPIO模块的寄存器进行配置,配置后的GPIO就可以对开发板上的按键状态进行观测,并对LED灯进行控制 -

AHB转APB桥(AHB2APB Bridge)

AHB2APB Bridge作为逻辑连接器,一方面是在AHB的Slave,另一方面也是APB的Master(APB总线有且只有这唯一1个Master)。

弄清这个概念,就可以定义模块的输入输出的端口,以及需要满足的时序。

由于AHB总线具有流水线特性,而APB没有,

因此需要Bridge在合适的时候拉低HREADY,添加一个AHB等待周期 -

通用输入输出模块(General-purpose Input/Output)

GPIO模块作为APB总线上的Slave,具有一个APB Slave接口,

除此之外,也会直接连接到FPGA开发板的按键外设和LED灯外设:

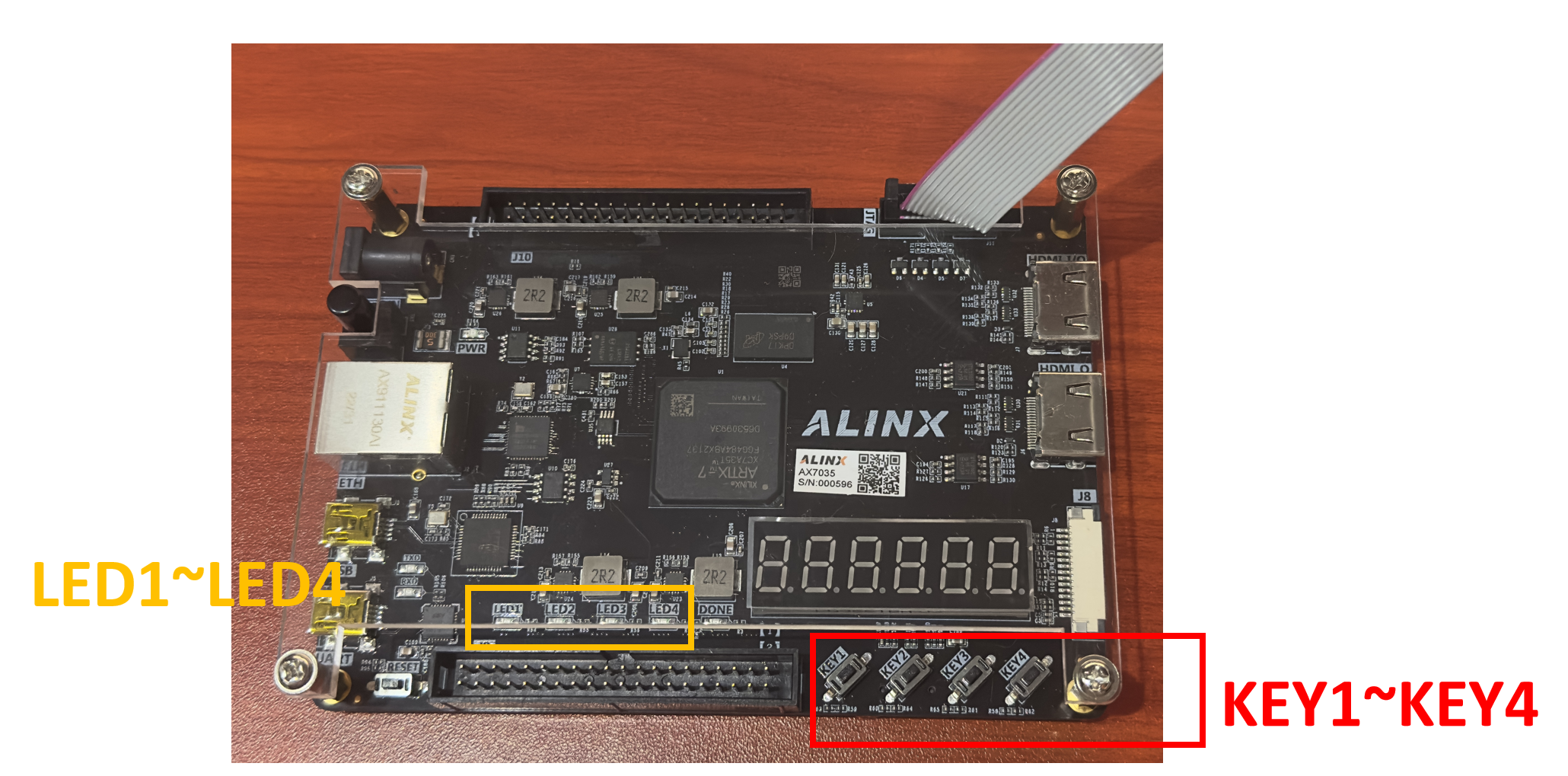

GPIO模块的输入端口Key[3:0],用于观测开发板上的按键状态,

GPIO模块的输出端口LED[3:0],用于控制开发板上LED灯的亮灭。

由于本项目用到的FPGA开发板的LED外设为共阳极,因此当引脚输出低电平时,对应LED将被点亮;反之,LED将会熄灭。

项目中涉及到的外设在开发板上的位置如下图所示:

1.2 流水灯系统工作模式

-

初始静止模式:所有LED灯熄灭,

上电后/按下reset后,进入该状态,所有LED灯熄灭,

此时LED_mode = 4'b0000(LED_mode为Control Unit中流水灯工作模式寄存器,用以控制LED灯闪烁的逻辑) -

工作模式0:普通流水灯模式

初始静止模式同时按下KEY0~KEY3进入工作模式0,

或在工作模式0~3下,按下FPGA开发板上按键KEY1进入工作模式0,

此时LED_mode = 4'b0001,

在工作模式0下,开发板上的LED灯将按照下图所示的方式,做有规律的周期性流动:

LED0~LED4将依次闪烁,每个灯闪烁时长为1s,循环周期为4s -

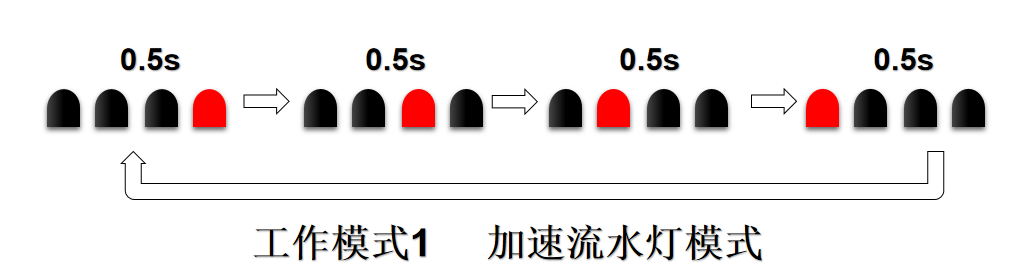

工作模式1:加速流水灯模式

在工作模式0~3下,按下FPGA开发板上按键KEY2,进入该工作状态,

此时LED_mode = 4'b0010,

在工作模式1下,LED灯将加速流动,每个灯闪烁时长为0.5s,循环周期为2s:

!

-

工作模式2:心跳模式

在工作模式0~3下,按下FPGA开发板上按键KEY3,进入该工作状态,

此时LED_mode = 4'b0100,

该模式下LED等将模仿心跳的节奏进行闪烁(详见最后一章中FPGA运行视频) -

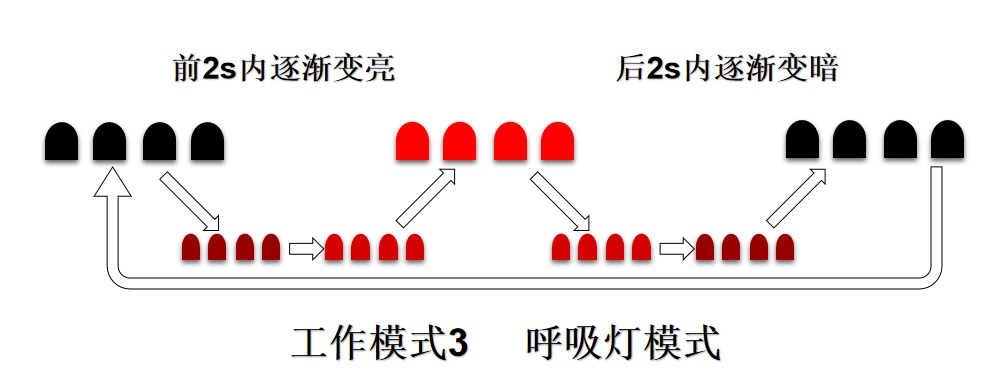

工作模式3:呼吸灯模式

在工作模式0~3下,按下FPGA开发板上按键KEY4,进入该工作状态,

该模式下LED将周期性进行逐渐由亮到暗再到亮的变化(周期为4s,其中前2s由暗变量,后2由亮变暗),

此时LED_mode = 4'b1000,

由于FPGA开发板上的LED灯亮度无法直接配置,

该模式是通过调节LED灯的占空比来实现的,占空比越高,小灯的平均功率越大,我们人眼看到的亮度也就越高

2. AHB2APB Bridge模块设计

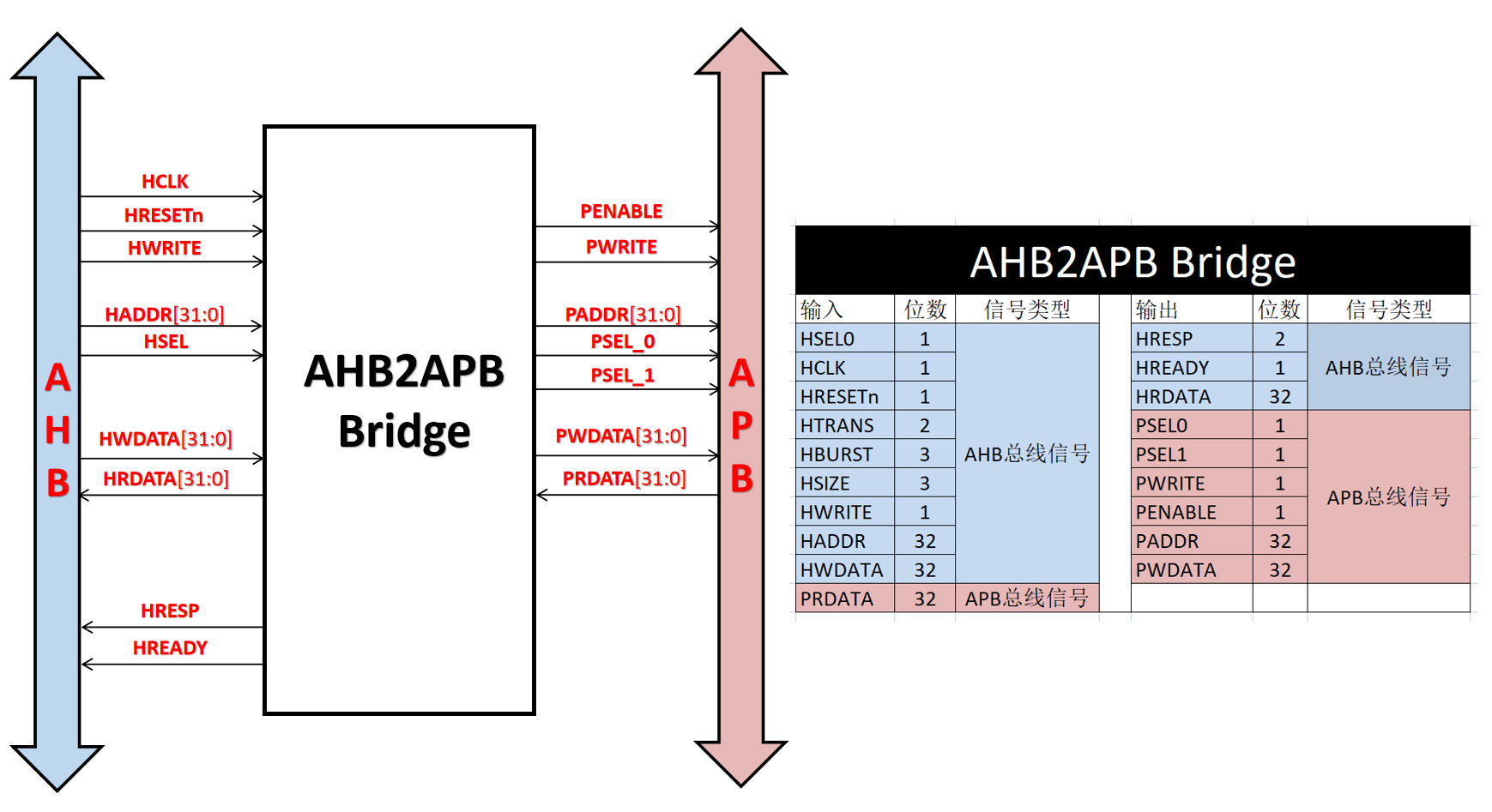

首先介绍AHB2APB Bridge模块的设计,

该模块是AHB与APB总线之间的桥梁,负责两种协议信号的相互转换,

AHB2APB Bridge的模块框图和信号定义如下:

AHB2APB Bridge既是AHB总线上的一个Slave,也作为APB总线上唯一的Master,

其任务是将来自于AHB总线上的信号转化为APB信号,实现AHB系统和APB的互联

2.1 AHB2APB Bridge原理与特性

AHB2APB Bridge模块的存