V_cnt <= 0;

else if(H_cnt == H_END - 1)

V_cnt <= V_cnt + 1'b1;

else

V_cnt <= V_cnt;

end

always @(posedge Clk or negedge Rst_n) begin

if(Rst_n == 0)

H_addr <= 0;

else if(H_cnt == H_DATA_END - 1)

H_addr <= 0;

else if(H_cnt >= H_DATA_BEGIN & DE_act == 1)

H_addr <= H_addr + 1'b1;

else

H_addr <= 0;

end

always @(posedge Clk or negedge Rst_n) begin

if(Rst_n == 0)

V_addr <= 0;

else if(V_cnt >= V_DATA_END - 1 & H_cnt == H_DATA_END - 1)

V_addr <= 0;

else if(V_cnt >= V_DATA_BEGIN & H_cnt == H_DATA_END - 1)

V_addr <= V_addr + 1'b1;

else

V_addr <= V_addr;

end

always @(posedge Clk or negedge Rst_n) begin

if(Rst_n == 0)

HS_act <= 1;

else if(H_cnt == H_PULSE_BEGIN )

HS_act <= 0;

else if(H_cnt == H_PULSE_END - 1)

HS_act <= 1;

else if(H_cnt == H_END - 1)

HS_act <= 0;

else

HS_act <= HS_act;

end

always @(posedge Clk or negedge Rst_n) begin

if(Rst_n == 0)

VS_act <= 1;

else if(V_cnt == V_PULSE_BEGIN)

VS_act <= 0;

else if(V_cnt == V_PULSE_END)

VS_act <= 1;

else if(V_cnt == V_END)

VS_act <= 0;

else

VS_act <= VS_act;

end

always @(posedge Clk or negedge Rst_n) begin

if(Rst_n == 0)

DE_act <= 0;

else if(H_cnt >= H_DATA_BEGIN - 1 & H_cnt <= H_DATA_END - 1 - 1 &

V_cnt >= V_DATA_BEGIN & V_cnt <= V_DATA_END - 1) // 这里H_DATA_END减两个1是通过仿真得出的结果。

DE_act <= 1;

else

DE_act <= 0;

end

always @(posedge Clk) begin

HS_reg[0] <= HS_act;

HS_reg[3:1] <= HS_reg[2:0];

VS_reg[0] <= VS_act;

VS_reg[3:1] <= VS_reg[2:0];

DE_reg[0] <= DE_act;

DE_reg[3:1] <= DE_reg[2:0];

end

assign HS = (HS_DELAY == 0)? HS_act : HS_reg[HS_DELAY - 1];

assign VS = (VS_DELAY == 0)? VS_act : VS_reg[VS_DELAY - 1];

assign DE = (DE_DELAY == 0)? DE_act : DE_reg[DE_DELAY - 1];

assign Disp_Pclk = Clk;

assign Disp_Red = (DE == 1)? RGB_Data[15:11] : 0 ;

assign Disp_Green = (DE == 1)? RGB_Data[10:5] : 0 ;

assign Disp_Blue = (DE == 1)? RGB_Data[4:0] : 0 ;

assign Data_Req = DE_act;

assign BL = 1'b1;

endmodule

二、仿真

1、仿真激励

`timescale 1ns / 1ps

module VGA_Display_tb();

reg clk_50m;

initial clk_50m <= 0;

always #10 clk_50m <= ~clk_50m;

reg rst_n;

initial begin

rst_n <= 0;

#200

rst_n <= 1;

end

wire Data_Req;

wire [11:0] H_addr;

wire [11:0] V_addr;

reg [15:0] RGB_Data;

wire [15:0] output_data;

wire Disp_Pclk;

wire HS;

wire VS;

wire DE;

wire BL;

always @(posedge clk_50m or negedge rst_n) begin

if(rst_n == 0)

RGB_Data <= 0;

else if(Data_Req)

RGB_Data <= RGB_Data + 1'b1;

else

RGB_Data <= RGB_Data;

end

VGA_Display

# ( .HS_DELAY (1),

.VS_DELAY (1),

.DE_DELAY (1))

VGA_Display_inst

(

//-----------内部接口------------

.Clk (clk_50m),

.Rst_n (rst_n),

.Data_Req (Data_Req),

.RGB_Data (RGB_Data),

.H_addr (H_addr),

.V_addr (V_addr),

//-----------外部接口------------

.Disp_Pclk (Disp_Pclk),

.Disp_Red (output_data[4:0]),

.Disp_Green (output_data[10:5]),

.Disp_Blue (output_data[15:11]),

.HS (HS),

.VS (VS),

.DE (DE),

.BL (BL)

);

endmodule

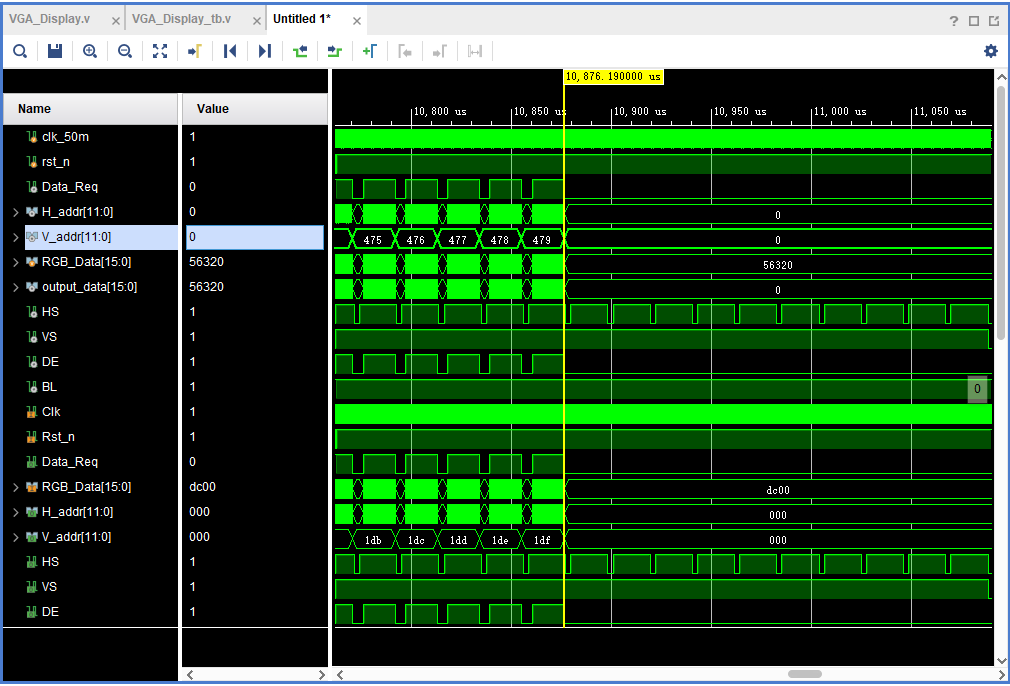

2、仿真分析

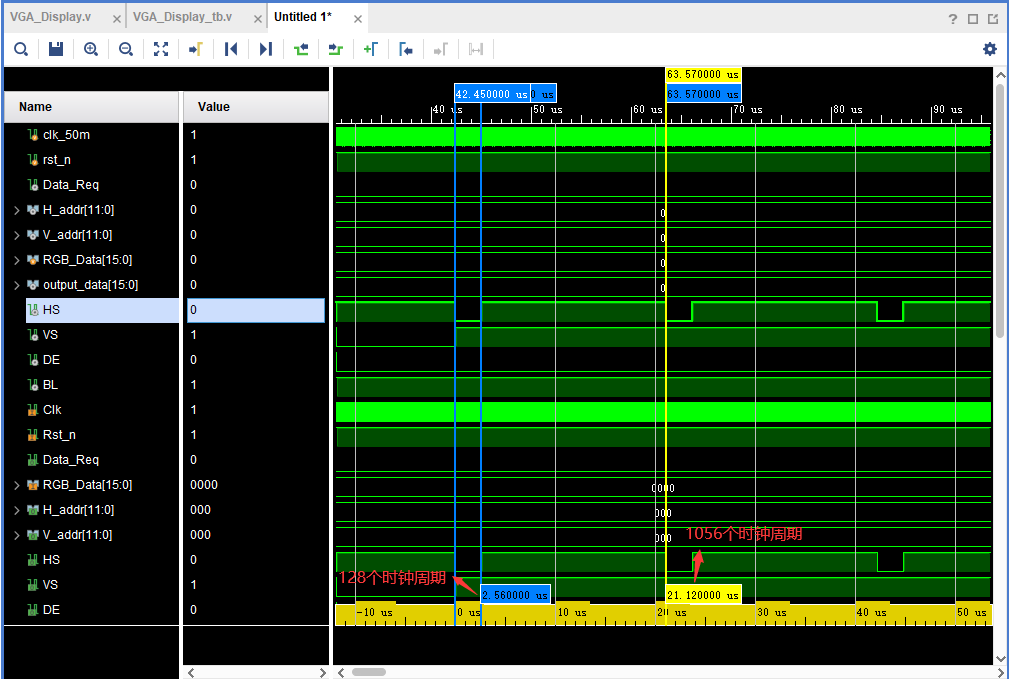

可见行时序符合参数设计。

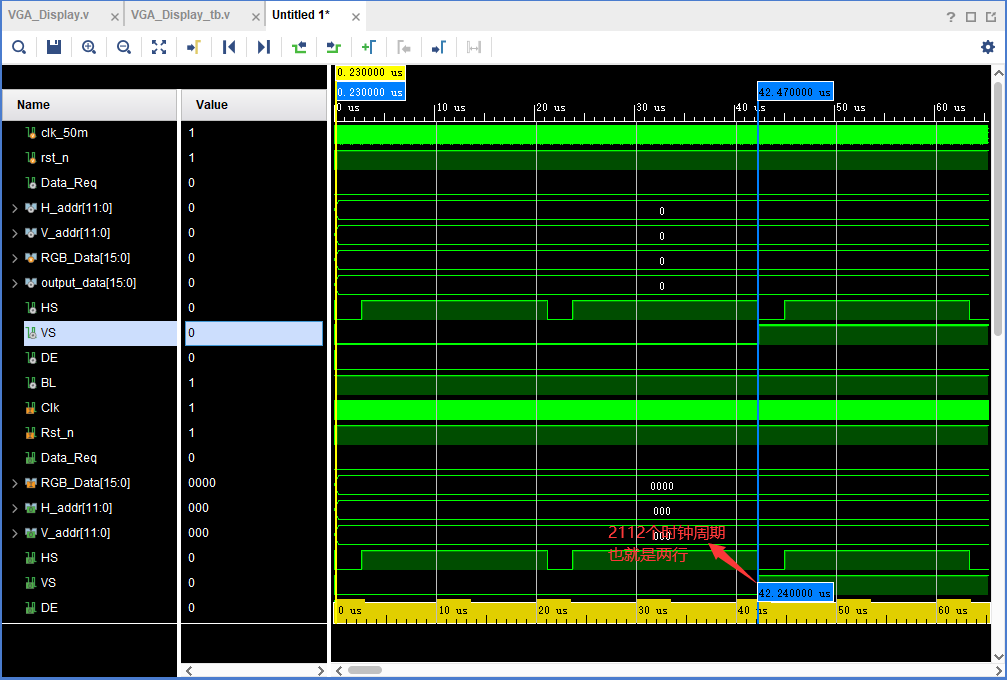

可见场时序也符合参数设计。

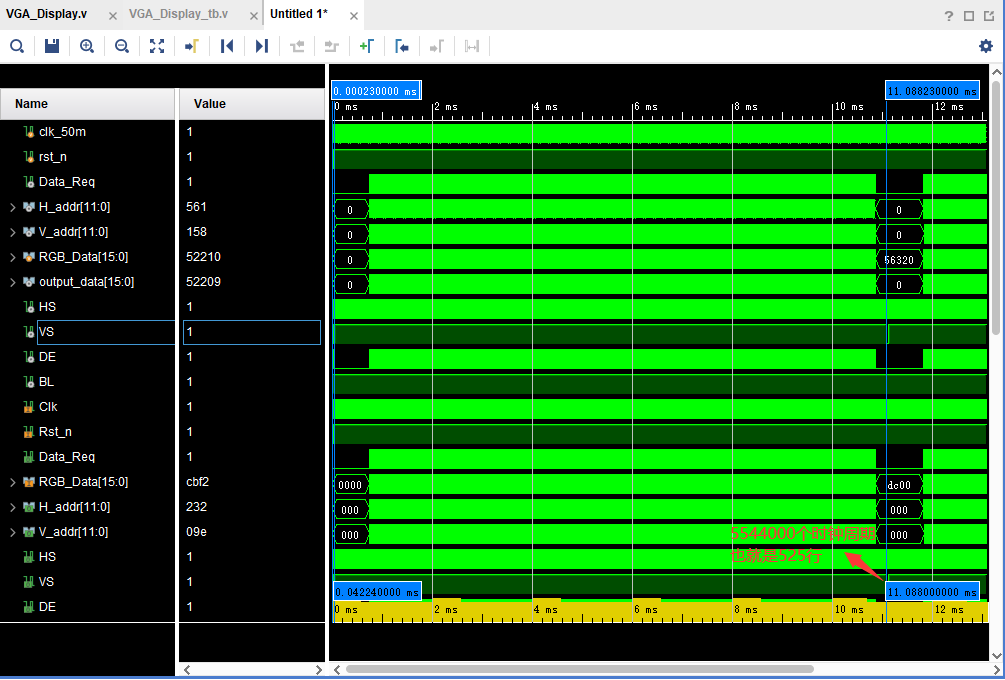

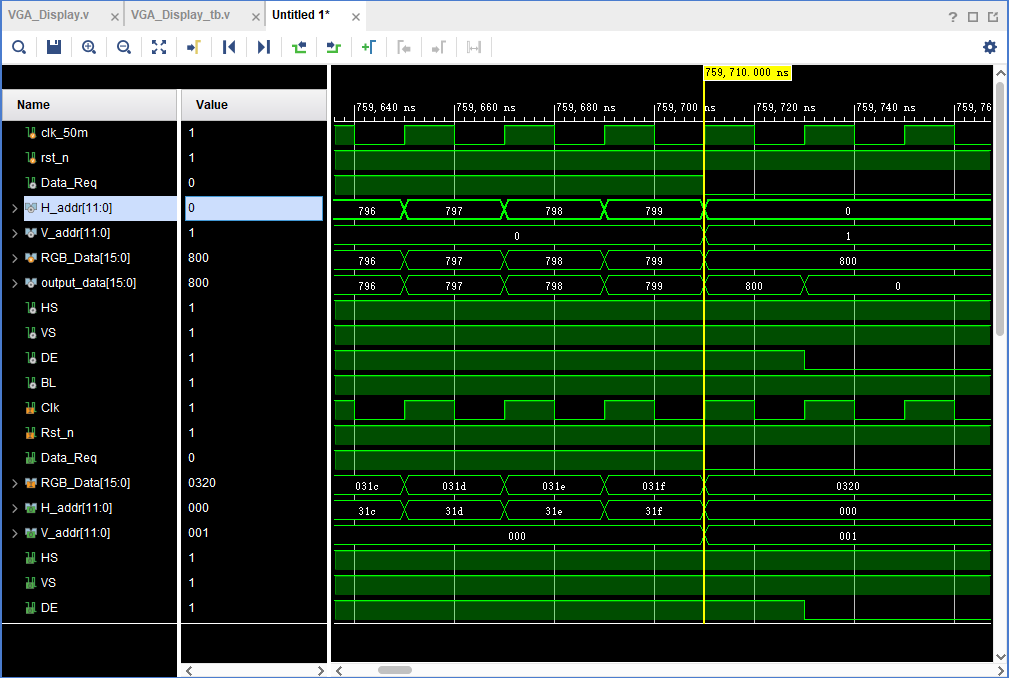

数据行地址从0计到799共800次

数据列地址从0记到479共480次

结论:仿真验证初步通过

三、上板验证

1、上板验证代码

此段代码中例化了一个时钟管理单元,输入为50M的时钟,输出为33M的时钟。

本模块设计预期为显示8个色块。

module VGA_TFT(

//内部信号

input CLK,

input Rst_n,

//外部信号

output Disp_HS,

output Disp_VS,

output [4:0] Disp_Red,

output [5:0] Disp_Green,

output [4:0] Disp_Blue,

output Disp_DE,

output Disp_PCLK,

output Disp_BL

);

reg [15:0] RGB_Data_in;

wire Data