FPGAФЪґ¦АнТмІЅРЕєЕК±Ј¬ѕЎБїґт1~2ЕДјДґжЖчЈ¬·сФтФЪПЯµчКФ»б·ўПЦёчЦЦЖж№ЦОКМвЎЈ

ПВГжКЗverilogґъВл

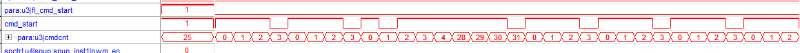

ФЪПЯµчКФ·ўПЦЈ¬јЖКэЖчФЪМш±д

ФТтКЗcmd_startУЙARMКдіцЈ¬УлFPGAК±ЦУТмІЅЈ¬РиТЄґт1~2ЕДјДґжЖч

reg [5:0] cmdcnt; reg fl_cmd_start; reg cmd_start_0,cmd_start_1; //-----------------------cmd_startВЛІЁ------------------//ЈЁARMКдіціЦРш580nsµДВціеЈ© //cmd_startОЄТмІЅРЕєЕЈ¬ХвАпґтБЅЕДјДґжЖчЈЁARMУлFPGAК±ЦУТмІЅЈ© always @(posedge clk_50m) begin cmd_start_0 <= cmd_start; cmd_start_1 <= cmd_start_0; end always@(posedge clk_50m or negedge rst_n) begin if(!rst_n) begin cmdcnt <= 6'd0; fl_cmd_start <= 0; end else begin if(cmd_start_1) begin if(cmdcnt==6'd24) fl_cmd_start <= 1'b1; cmdcnt <= cmdcnt + 1'b1; end else begin cmdcnt <= 6'd0; fl_cmd_start <= 0; end end end

ХвСщРЮёДєуІ»»біцПЦјЖКэТміЈМш±д