FPGA 的详细开发流程就是利用 EDA 开发工具对 FPGA 芯片进行开发的过程。

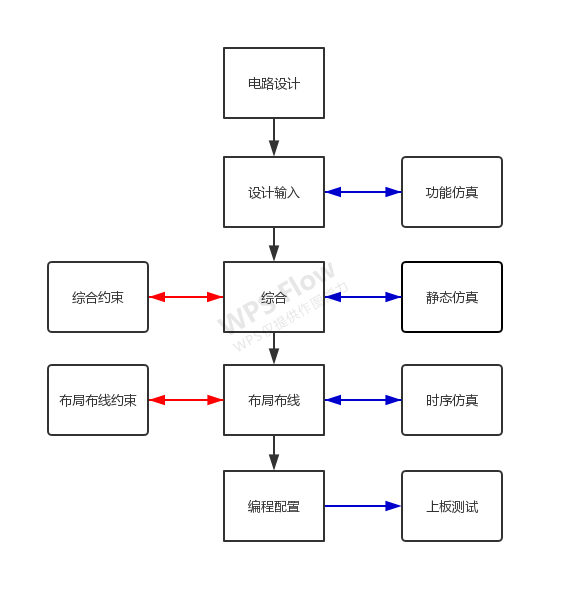

FPGA 的详细开发流程如下所示,主要包括电路设计、设计输入、综合(优化)、布局布线(实现与优化)、编程配置五大步骤,其中,还有功能仿真、静态仿真、时序仿真三大仿真,以及综合约束、布局布线约束(包括位置约束和时序约束)两大约束等等。

1、电路设计(FPGA Design)

在电路设计之前,首先要进行的是算法的设计与验证(在 Python 或 Matalb 中完成)(至于算法是怎么来的,一般是根据市场需求来开发的,这个就不在本次讨论之中了)、方案论证、架构设计和 FPGA 芯片选型等准备工作。系统工程师根据任务要求,如系统的指标和复杂度、成本、功能性和稳定性、性能、对工作速度(延时和工作频率)和芯片本身的各种资源、功耗等等方面进行权衡(蓝色加粗部分也是数字电子系统的五大设计目标),选择合理的设计方案(浮点定点、设计优化)和合适的 FPGA 器件类型(如 Cylone、Spartan、Artix、Virtex、Kintex、还是 Zynq 或者是 Zynq UltraScale + 等等)。

电路设计方法分为自底向上和自顶向下的设计方法。一般都采用自顶向下的设计方法(从系统设计开始,逐渐向模块设计、器件设计和版图设计等更物理的层次推进):从系统设计开始入手,然后把整体系统分成若干个基本单元,然后再把每个基本单元划分为下一层次的基本单元,一直这样做下去,直到可以直接使用 EDA 元件库为止。最后,才开始 Coding。

2、设计输入(Design Entry)

设计输入指的是将设计者所涉及的电路以开发软件要求的某种形式表达出来,并输入到相应的软件中的过程。最常见的设计输入的表达方式为 IP 核、原理图(Schematic)和 HDL 文本输入。

这里的 IP 按照来源的不同可以分为三类,第一种是来自前一个设计的内部创建模块(Design by Yourself),第二种是 FPGA 厂家,第三种就是来自 IP 厂商。而按照产品交付的形式,IP 核又分为软核(HDL 形式描述的功能块)、硬核(版图形式:提供设计的最终阶段产品,即掩膜)、固核(网表形式:完成了综合的功能块)。

FPGA 厂家和 IP 厂商可以在 FPGA 开发的不同时期提供给我们不同的 IP。我们暂且知道他们分别是未加密的 RTL 级 IP、加密的 RTL 级 IP、未经布局布线的网表级 IP、布局布线后的网表级 IP。

3、综合(Synthesis)

综合一般指的是将高级抽象层次的设计描述自动转化为较低层次描述的过程。而在 FPGA 中的综合则是指自动实现如下转换的软件工具,或者说,综合器就是能够将原理图或者 HDL 文本语言、描述的电路编译成由与或阵列、RAM、触发器、寄存器等逻辑单元组成的电路结构网表的工具。

综合包括编译、映射和优化(也可以分开不被综合所包含),编译就是 HDL → 门级网表,映射就是门级网表 → LUT,优化就是优化设计( 需要说明的是在 Altera 的开发流程中,将编译、映射过程按照我们叙述的合称为综合,而在 Xilinx 的开发流程中,由设计输入得到门级网表的过程叫做综合,而映射过程归结到其叫做实现的某一子步骤中。不过这都是小问题,整体的流程还是遵循这个顺序的)。

综合的形式:

1、将算法、行为描述转换到 RTL 级(Register Transfer Level)(寄存器传输级),即从行为描述到结构描述。

2、将 RTL 级描述转换到逻辑门级(包括触发器),称为逻辑综合。

3、将逻辑门表示转换到版图表示,或者 PLD 器件的配置网表表示;根据版图信息能够进行 ASIC 生产,有了配置网表可完成基于 PLD 器件的系统实现。

这边介绍一下数字系统设计器件:

数字系统器件的实现从以前的 PLA(可编程逻辑阵列)、PAL(可编程阵列逻辑)、GAL(通用阵列逻辑)发展到如今的 PLD(可编程逻辑器件 Programmable Logic Device)(包括现场可编程门阵列 FPGA(Field Programmable Gate Array)和复杂可编程逻辑器件 CPLD(Complex Programmable Logic Device))(半定制)、ASIC(专用集成电路 Application Specific Integrated Circuits)(全定制)。

软件程序编译器是将 C 或汇编语言等编写的程序编译为 0,1 代码流,而硬件综合器是将 Verilog HDL 等语言编写的程序转化为具体的电路网表结构。

在电路设计中,网表(Netlist)是用于描述电路元件相互之间连接关系的,一般来说是一个遵循某种比较简单的标记语法的文本文件。(百度百科 门级网表)。综合就是逻辑综合器根据约束条件把 Verilog HDL 或 VHDL 描述的 RTL 级设计,转换为可与 FPGA/CPLD 的门阵列基本结构相映射的网表文件。

4、布局布线(Place & Route)

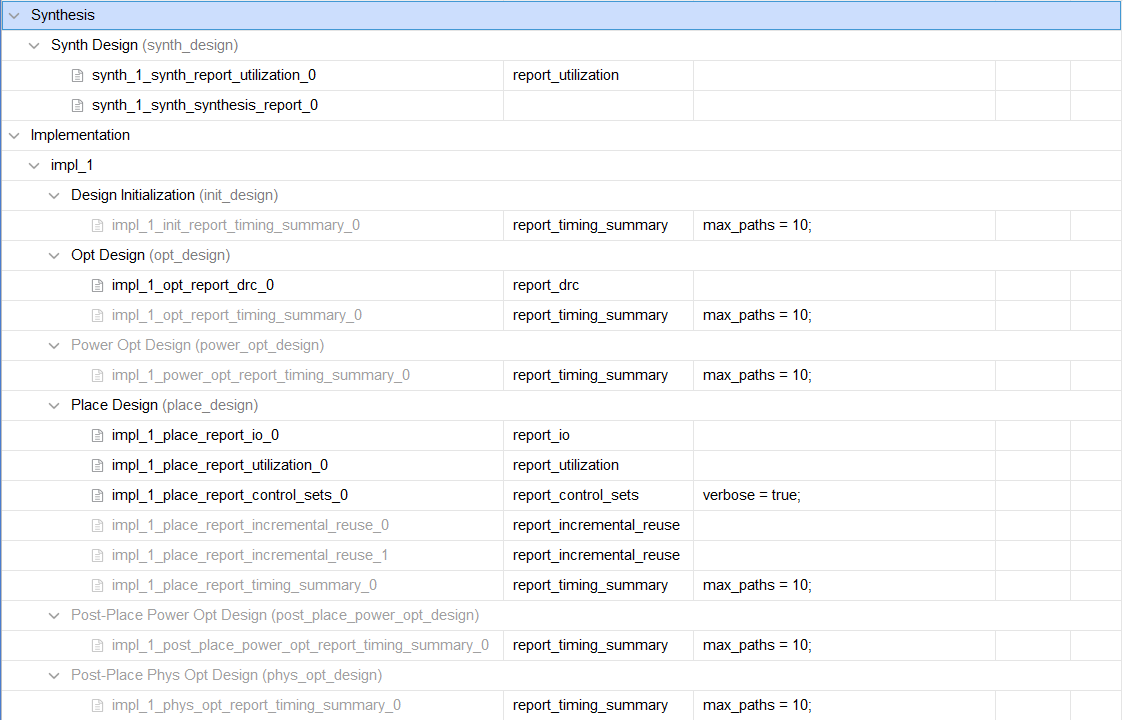

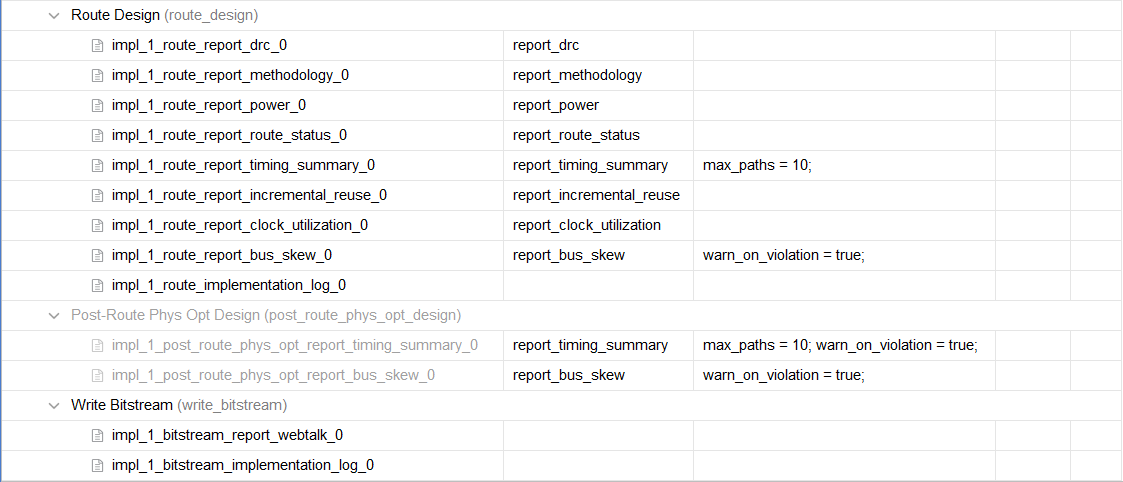

谈及布局布线之前,首先要谈到实现(Implementation)。实现就是将综合生成的逻辑网表配置到具体的 FPGA 芯片上,而布局布线就是其中最重要的过程。Vivado 中的实现具体如下所示,分为设计初始化(Design Initialization)、优化设计(Opt Design)、功耗优化设计(Power Opt Design)、布局设计(Place Design)、后布局功耗优化设计(Post-Place Power Opt Design)、后布局物理优化设计(Post-Place Phys Opt Design)、布线设计(Route Design)、后布线物理优化设计(Post-Route Phys Opt Design)、生成比特流(Write Bitstream)。

布局布线指的是将综合生成的电路逻辑网表映射到具体的目标器件中实现,并产生最终的可下载文件的过程。

布局是将已分割的逻辑小块放到器件内部逻辑资源的具体位置,并使它们易于连线;

布线则是利用器件的布线资源完成各功能模块之间和反馈信号之间的连接。

布局布线完成之后将产生如下一些重要的文件:

1、芯片资源耗用情况报告。

2、面向其他 EDA 工具的输出文件,如 EDIF 文件等。

3、产生延时网表结构,以便于进行精确的时序仿真,这时候的仿真结果能够比较精确地预测未来芯片的实际性能。如果仿真结果达不到设计要求,就需要修改源代码或者选择不同速度的器件,直至满足设计要求,例如普通加法器改为超前进位加法器,普通乘法器改为 Booth 乘法器等等,通过减少关键路径来满足时序要求。

4、器件编程文件:如用于 FPGA 配置的 SOF,JAM,BIT 等格式的文件,用于 CPLD 编程的 JEDEC,POF 等格式的文件。由于布局布线与芯片的物理结构直接相关,所以一般选择芯片制造商提供的开发工具进行此项工作。

约束(Constraint)(附加):

约束分为综合约束和布局布线约束,布局布线约束又可以分为位置约束、时序约束。约