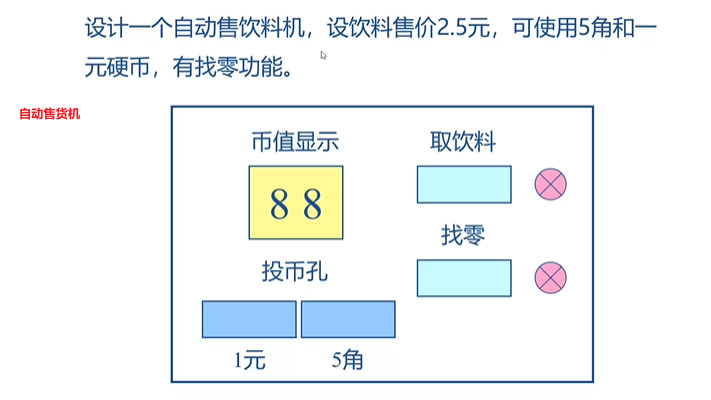

гаЯозДЬЌЛњ

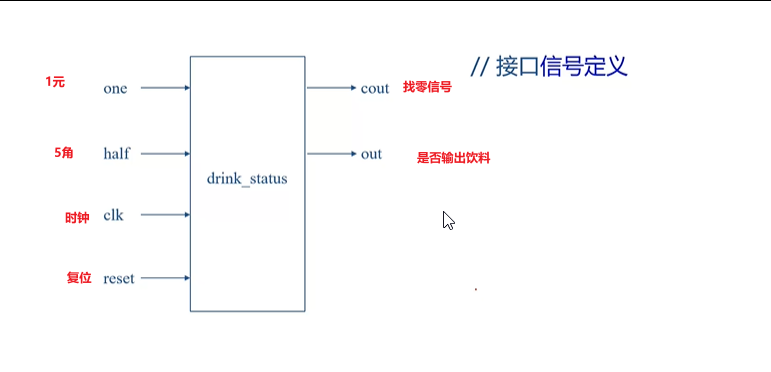

аДRTLЕФЪБКђ,ЪЕЯжвЛИіЙІФмЕФЪБКђгаКмЖржжЗНЗЈ

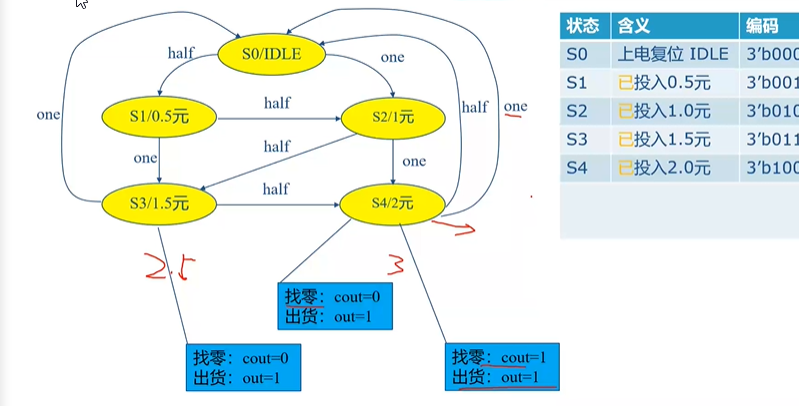

- НЋЯЕЭГЛЎЗжЮЊЖрИізДЬЌ,зДЬЌжЎМфгазДЬЌЕФзЊвЦ,ЕквЛВН,ЕкЖўВН,,,,аЮГЩгаЯозДЬЌЛњ

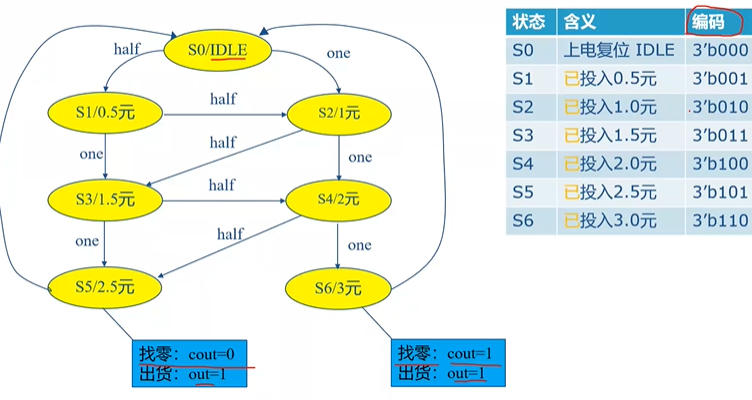

- СїЫЎЯпММЪѕЩшМЦ,ДгЪфШыЕНЪфГігаЖрИіВНжш

гаЯозДЬЌЛњ,зДЬЌЪЧгаЯоЕФ,БШШч8ИізДЬЌ,16ИізДЬЌЕШ,дкНјааЩшМЦЕФЪБКђ,зДЬЌЛњЕФзДЬЌВЛвЊЬЋЖр,зДЬЌГЌЙ§10Иі,ОЭЛсдьГЩЩшМЦИДдгЖШКЭбщжЄИДдгЖШЖМБфИп.

гаЯозДЬЌЛњЗжРр

- Moore FSM

ЪфГіжЛгыЕБЧАЕФзДЬЌгаЙи,гыЪфШыУЛгаЙиЯЕ - Mealy FSM

ЪфГіВЛНігыЕБЧАЕФзДЬЌгаЙи,ЛЙгыЪфШыгаЙи

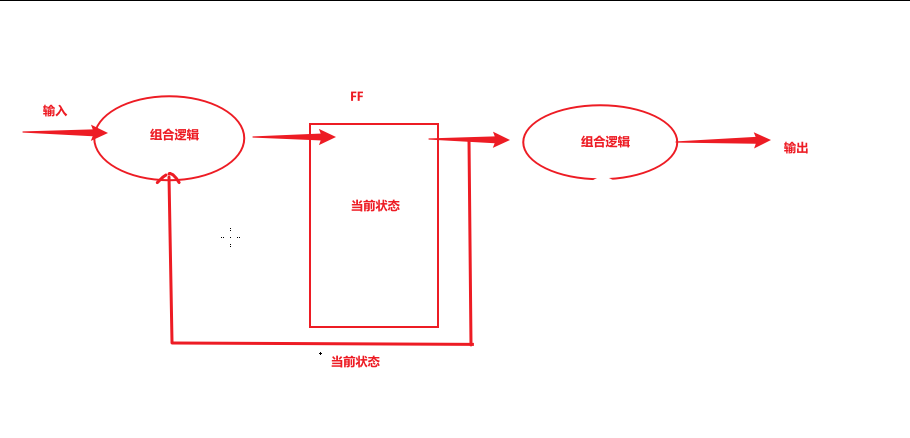

Moore FSM-ЩшМЦздЖЏЪлЛѕЛњ

ЗжЮіЪфШыЪфГіаХКХ

- здЖЏЪлЛѕЛњ,ЪфШыЕФОЭЪЧгВБв,ЪфГіЕФЪЧвћСЯКЭевСу (ШЗЖЈЪфШы,ЪфГі)

- МйЩшвћСЯжЛгавЛжжМлИё2.5дЊ,ЪфШыЕФСуЧЎжЛгавЛдЊКЭЮхНЧ(СНжжзДЬЌ,гУ1bitБэЪО),евСуЕФЧщПіжЛгаСНжж0дЊКЭ5НЧ(гУ1bitБэЪО)(ШЗЖЈЪфГіЪфГіЕФзДЬЌ,гУМИЮЛЕФаХКХБэЪО)

ЖЈвхНгПк

- зДЬЌЛњвЊДцДЂвЛаЉзДЬЌ,ПЯЖЈЛсгавЛаЉМФДцЦї,ЛсгаЪБжгКЭИДЮЛаХКХ

- дкЩшМЦвЛИіФЃПщЕФЪБКђ,зюЯШШЗЖЈЪфШыЪфГіЕФЖЫПкКЭЮЛПэвдМАЪБађ

ЖЈвхЪБађ

- ЪфШыЕФвЛдЊКЭЮхНЧВЛФмЭЌЪБЮЊ1(ШЗЖЈЪфШыЕФдМЪј)

ФкВПЪЕЯж--ЛГізДЬЌзЊвЦЭМ

вЊДцДЂЕБЧАвбОДцДЂСЫЖрЩйЧЎ,ГѕЪМзДЬЌЪБ0,ПЩвдЪеЕН1дЊКЭ5НЧ

- IDLEОЭЪЧЕБЧАЯЕЭГЪЧПеЯазДЬЌ,УЛгаЪеЕНШЮКЮЕФЭЖБв

- етЪЧвЛИіMooreРраЭЕФгаЯозДЬЌЛњ,ЪфГіжЛгыЕБЧАЕФзДЬЌгаЙи

MooreгаЯозДЬЌЛњЕчТЗЬиЕу

- ЪфШыгыЕБЧАЕФзДЬЌгаЙи,ЫљвдашвЊвЛИіМФДцЦїДцДЂЕБЧАЕФзДЬЌ

- МФДцЦїДцДЂЕФзДЬЌЪфШыИјзщКЯТпМжЎКѓ,НјааЪфГі

- ЪфШыгыЕБЧАЕФзДЬЌжЕ,ОЙ§зщКЯТпМжЎКѓ,ЪфШыИјМФДцЦї

- ЪБађЧхЮњ,ЪфШыКЭЪфГі,УЛгавЛЬѕжБНгЕФзщКЯТпМТЗОЖ;ШчЙћЪфШыОЙ§зщКЯТпМ,УЛгаОЙ§МФДцЦї,жБНгЪфГі,етбљЕФЩшМЦВЛКУ;вђЮЊВЛжЊЕРжмЮЇЛЗОГЕФзщКЯТпМЕФЪБађЪЧЖрЩй

Code

module drink_status_moore(

input clk,

input reset,

input half,

input one,

output out,

output cout

);

parameter [2:0] s0 = 3'b000,

s1 = 3'b001,

s2 = 3'b010,

s3 = 3'b011,

s4 = 3'b100,

s5 = 3'b101,

s6 = 3'b110; //ЖЈвх6ИізДЬЌ

reg [2:0] curr_state; //ЕБЧАзДЬЌ CS

reg [2:0] next_state; //ЯТвЛИізДЬЌ NS regЖЈвхЕФаХКХВЛвЛЖЈЪЧМФДцЦї

//ЕквЛЖЮ:ЩљУївЛИіМФДцЦї,state transfer

always @ (posedge clk ,negedge reset) begin

if(~reset)

curr_state <= s0; //етРяЪБжгРДСЫжЎКѓ,ОЭМФДцЦїДЋЪф,МФДцЦїЙІКФБШНЯДѓ,ашвЊИјМФДцЦїДЋЪфЬэМгЬѕМў

else

curr_state <= #1 next_state;

end

//ЕкЖўЖЮ,ИљОнЬѕМўаДГіжаМфзДЬЌзЊвЦ

always @ (curr_state,half,one) begin

case(curr_state)

s0:begin

if(half) next_state = s1; //ШчЙћСНИіЭЖБвПк,ОЭЛсГіЯжЮЪЬт,вЛДЮЭЖШыПЩФмЮЊ1.5дЊ,ЫљвдвЊИјЪфШыЬэМгдМЪј

else if(one) next_state = s2; //ЮФМўКЭЮФМўжЎМфашвЊНјаавЛаЉдМЪј

else next_state = S0;

end

s1:begin

if(half) next_state = s2;

else if(one) next_state = s3;

else next_state = S1;

end

s2:begin

if(half) next_state = s3;

else if(one) next_state = s4;

else next_state = S2;

end

s3:begin

if(half) next_state = s4;

else if(one) next_state = s5;

else next_state = S3;

end

s4:begin

if(half) next_state = s5;

else if(one) next_state = s6;

else next_state = S4;

end

s5:begin

next_state = s0;

end

s6:begin

next_state = s0;

end

default: next_state = s0;

end

//ЕкШ§ЖЮ,аДГіЪфГі

assign out = (curr_state == s5) || (curr_State = s6) ? 1:0;

assign cout = (curr_state == s6) ? 1:0;

endmodule

FSM Ш§ЖЮЪНЕФЪщаДЗНЪН

mealy FSM-здЖЏЪлЛѕЛњ

- ЯрЕБгкдкЕБЧАзДЬЌ,ПМТЧжЎКѓЪфШыЕФзДЬЌ

- ЪфШыОЙ§зщКЯТпМжЎКѓжБНгЕУЕНЪфГі

module drink_status_moore(

input clk,

input reset,

input half,

input one,

output out,

output cout

);

parameter [2:0] s0 = 3'b000,

s1 = 3'b001,

s2 = 3'b010,

s3 = 3'b011,

s4 = 3'b100; //ЖЈвх6ИізДЬЌ,БфСПУћашвЊИќМгОпгаКЌвх

reg [2:0] curr_state; //ЕБЧАзДЬЌ CS

reg [2:0] next_state; //ЯТвЛИізДЬЌ NS regЖЈвхЕФаХКХВЛвЛЖЈЪЧМФДцЦї

//ЕквЛЖЮ:ЩљУївЛИіМФДцЦї,state transfer

always @ (posedge clk ,negedge reset) begin

if(~reset)

curr_state <= s0; //етРяЪБжгРДСЫжЎКѓ,ОЭМФДцЦїДЋЪф,МФДцЦїЙІКФБШНЯДѓ,ашвЊИјМФДцЦїДЋЪфЬэМгЬѕМў

else

curr_state <= #1 next_state;

end

//ЕкЖўЖЮ,ИљОнЬѕМўаДГіжаМфзДЬЌзЊвЦ

always @ (*) begin

case(curr_state)

s0:begin

if(half) next_state = s1; //ШчЙћСНИіЭЖБвПк,ОЭЛсГіЯжЮЪЬт,вЛДЮЭЖШыПЩФмЮЊ1.5дЊ,ЫљвдвЊИјЪфШыЬэМгдМЪј

else if(one) next_state = s2; //ЮФМўКЭЮФМўжЎМфашвЊНјаавЛаЉдМЪј

else next_state = S0;

end

s1:begin

if(half) next_state = s2;

else if(one) next_state = s3;

else next_state = S1;

end

s2:begin

if(half) next_state = s3;

else if(one) next_state = s4;

else next_state = S2;

end

s3:begin

if(half) next_state = s4;

else if(one) next_state = s0;

else next_state = S3;

end

s4:begin

if(half) next_state = s0;

else if(one) next_state = s0;

else next_state = S4;

end

default: next_state = s0;

endcase

end

//ЕкШ§ЖЮ,аДГіЪфГі

assign out = ((curr_state == s4) &am