最近在写一本Xilinx的FPGA方面的书,现将HLS部分内容在这里分享给大家,希望大家喜欢,也欢迎批评指正。以下原创内容欢迎网友转载,但请注明出处: https://www.cnblogs.com/helesheng

在可编程逻辑器件被用于电子系统设计的前期,由于所含的逻辑资源较少,绝大部分情况下,它们被用于实现数据的传输和接口电路。工程师们习惯于使用寄存器传输级(RTL)的描述方式来开发可编程逻辑器件,以提高对逻辑资源的利用率。但正如我们在前面的章节中看到的,使用Verilog HDL这样的硬件描述语言进行RTL级的开发是一件非常费时、费力的事。

另一方面,随着摩尔定理的不断发展,集成在可编程逻辑器件中的逻辑资源呈指数级的快速增长,对于开发者而言节约器件中的逻辑资源的重要性不断降低。与此同时,随着深度学习算法和软件无线电(SDR)技术的成熟,可编程器件中需要由硬件实现的算法越来越复杂。再使用硬件描述语言低效率的实现这些复杂的算法,越来越无法满足时长对产品上市的时间要求。

提升可编程逻辑器件开发速度的方法无非有二:1、使开发工具能够自动处理尽可能多的细节,降低项目开发时间(提升抽象的层级)。2、同一段代码经过简单地修改就能够适用不同器件和优化要求,从而被尽可能多的项目使用(设计的重用)。而Vivado High Level Synthesis(高层次综合器,简称HLS)正式Xilinx在上述思路指导下设计的一种开发工具,它通过直接使用C、C++或System C等高级语言进行硬件开发,能够大幅度提升算法开发的抽象层次和设计重用率的高效开发工具。

8.1 高层次综合器(HLS)的概念与特点

1. 为什么需要高层次综合器

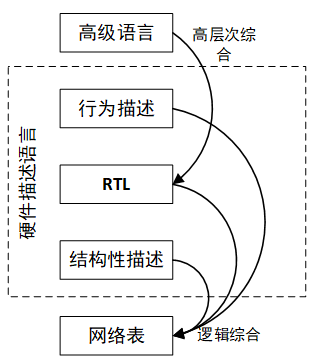

FPGA开发工具发展的一个总趋势是提高描述数字系统的抽象层级,从而隐藏更多的底层技术细节,以达到提高复杂算法开发的效率和不同器件之间设计重用的目的。在本书前述的硬件描述语言Verilog HDL能够实现的抽象,由低到高包括:结构级的抽象、寄存器传输级抽象和行为级的抽象。其中结构级的抽象直接描述查找表和寄存器的连接和配置;寄存器传输级的抽象只描述寄存器与寄存器之间的可以被解释和执行的操作,隐藏了具体的连接和配置方法,而将这部分细节留给硬件描述语言自动补齐;Verilog HDL能够实现的最高级别的抽象称为“行为级”,在这个级别上,硬件描述语言的综合器可以直接针对设计者所需要的电路行为和算法产生所需的电路,从而隐藏了大部分的电路细节。

而所谓“高层次综合器”完全摆脱了电路水平的硬件描述,开发者只需要通过C、C++和System C等传统意义上的计算机高级语言来描述算法本身,而不必过分关注硬件电路及其在FPGA内部的实现方式。从FPGA开发工具角度来理解,高层次综合器非上平行于硬件描述语言(HDL)的上述抽象层级(结构级、寄存器传输级和行为级)的独立描述层级。因为,高层次综合器的作用是将高级语言描述的算法和行为综合成寄存器传输级描述的硬件描述语言,再由Vivado以调用IP的形式,调用这些寄存器传输级的硬件描述语言,并将其进一步综合成FPGA可以直接使用的网络表。因此,高层次综合器的“综合”与硬件描述语言的“综合”的内涵并不相同,高层次综合器(HLS)也不能独立于Vivado单独使用。下图所示的是高层次综合器(HLS)的综合和硬件描述语言(HDL)的综合之间的关系,理解这幅图,有利于读者理解高层次综合器开发和优化流程。

图8.1 .1 高层次综合器(HLS)的综合和硬件描述语言(HDL)的综合之间的关系

总体而言,高层次综合器由于使用了更高层级的描述抽象,将更多的电路查找表和寄存器的连接、配置,以及信号传输的细节甩给了开发工具来自动完成,符合FPGA开发工具发展的趋势。虽然在这个过程中可能由于开发工具无法深刻理解具体应用的需求,从而导致FPGA资源的部分浪费,但带来的优势也非常明显:

其一,开发者无需关注细节的实现,导致开发效率成倍增加;开发者能够将精力放在对系统而言更加重要的算法开发上。

其二,用高级语言开发的算法代码,最大程度的做到了与具体器件“脱钩”,是的同一段代码经过简单的移植后就能够适用于使用不同器件的工程,提升了代码的重用率。

其三,在不同的项目中使用同一种算法时,可能会由于不同项目对算法执行时间和逻辑资源的要求不同,造成代码重复开发的问题。而高层次综合器HLS能够通过简单的配置,实现对同一段代码优化策略的重配置,进一步提升了代码的重用率。

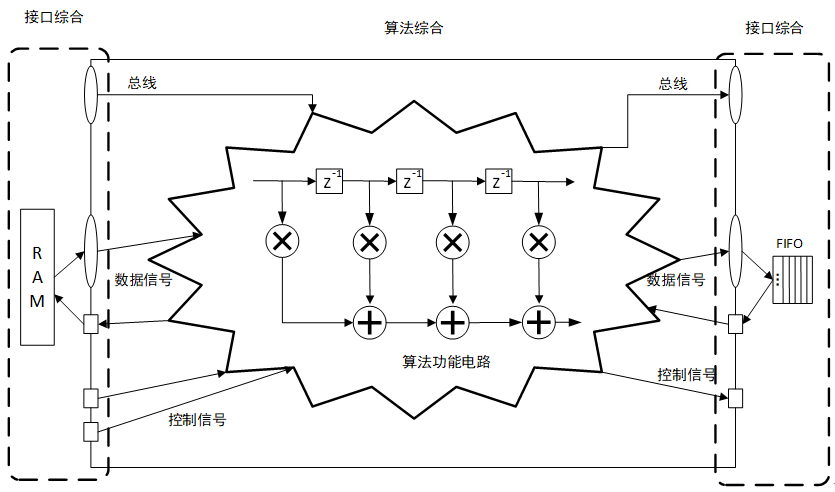

2. 高层次综合器产生的电路模块

如图8.1.1所示,高层次综合器是一种能够将传统的高级语言描述的算法,转换为在可编程逻辑器件上实现的硬件描述语言的高效率开发工具。但一旦仔细推敲,细心的读者就会发现,传统的C/C++这类高级语言是建立在执行程序的CPU“逐条”取指执行的图灵机框架下的;而实现在可编程器件上的硬件电路却是相对固定,且需要实实在在接口硬件来完成算法数据的输入和结果输出的。因此高层次综合器的功能必然包括产生以下两部分电路:算法功能性电路,以及接口(也称为“顶层连接”)电路两个部分。图8.1.2所示的是一个典型的高层次综合器完成的硬件设计,其中包含了算法综合(Algorithm Synthesis)产生的功能性电路,以及接口综合(Interface Synthesis)产生的输入输出电路。而这两部分也是设计者使用高层次综合器开发时,需要根据要求着重设计和斟酌的。

图8.1.2 高层次综合器产生的典型电路

3. 使用高层次综合器的开发流程

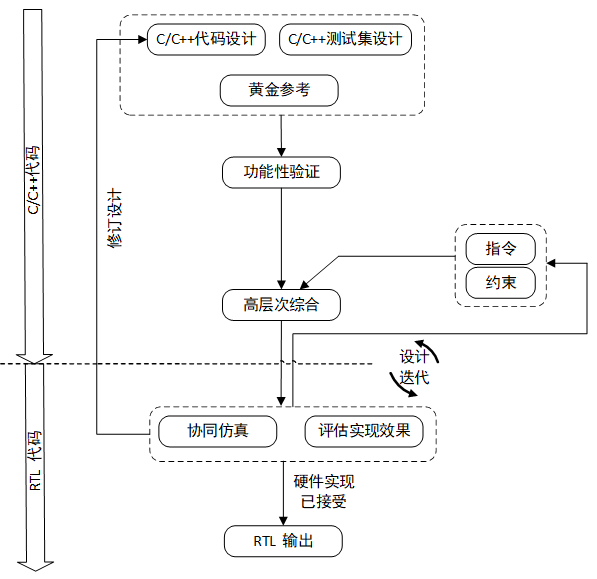

使用高层次综合器进行开发的流程模型如下图所示。

图8.1.3 高层次综合器开发流程示意图

1)开发者需要给高层次综合器的,首先是一个能够实现所需算法功能的C/C++函数;其次是一个用于测试和验证该函数的标准输入和输出数据和调用该函数的代码。也就是上图中的“黄金参考”和“C测试集”(在很多设计中黄金参考被以数据的形式写入到C测试集的C/C++代码中)。

2)有了黄金测试和C测试集后,高层次综合器就可以进行功能性验证了。而通过功能性测试的算法函数代码就可以进入到高层次综合器的“本质工作”高层次综合阶段了。此时开发者可以通过图形化窗口或指令的方式配置图8.1.3所示的“算法综合”和“接口综合”的硬件细节。高层次综合完成后,将产生以硬件描述语言的RTL模型,包括HDL文件和所需的各种日志、输出文件,测试集、脚本等设计文件。

3)高层次综合器产生的RTL模型不一定与算法的预期设计完全相同,这就需要对RTL模型进行协同仿真。此时需要再次用C测试集,对RTL模型进行仿真,并比较仿真输出和黄金参考的差异。另外,在上图中的C/RTL协同仿真的同时,还可以对硬件实现所需的资源的数量、执行的延迟、最高工作时钟频率等进行“实现的评估”。若实现无法达到设计