end

end

endmodule

6.3 Tsetbench

`timescale 1ns/1ps

module clk_div_FSM_tb;

//信号申明

reg clk;

reg rst_n;

wire clk_FSM;

parameter DIV_CLK = 5; //定义源时钟信号一周期时间

//复位信号生成

initial begin

clk = 0; //时钟信号赋初值

rst_n = 1; //复位信号赋初值

#(3*DIV_CLK)

rst_n = 0;

#(6*DIV_CLK)

rst_n = 1;

#(20*DIV_CLK);

end

//源时钟信号生成

always #DIV_CLK clk = ~clk;

//模块例化

clk_div_FSM u_clk_div_FSM

(.clk (clk),

.rst_n (rst_n),

.clk_FSM (clk_FSM)

);

endmodule

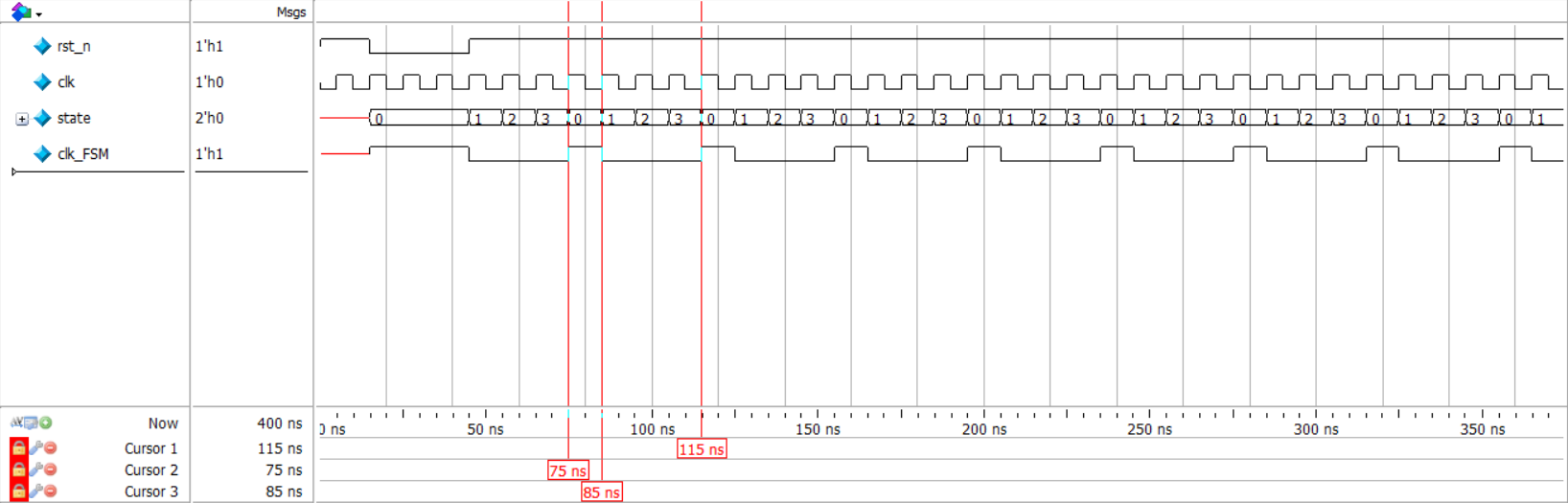

6.4仿真结果

七、总结

偶数分频:无论是通过D触发器还是计数器实现,这类分频都是最容易得到的,并且占空比容易控制在50%。对于D触发器实现偶数分频来说,分频数只能得2^n,其余分频数只能由计数器法等其他方法实现。除此以外,随着分频的数目不断增大,通过D触发器实现触发器数目会增多,在电路设计的过程中应当考虑面积因素。对于计数器实现偶数分频,占空比和分频数都可以得到极大的控制,是实现偶数分频最灵活的一种方式。

奇数分频:计数分频基本原理也是通过计数器实现的,主要分为占空比非50%的奇数分频和占空比50%的奇数分频,后者实现简单而后者稍稍复杂一些。占空比非50%的情况下,时钟信号在上升沿(N-1)/2翻转和 0翻转即可得到需要的分频信号。占空比50%的情况下,一个时钟信号在上升沿而一个时钟信号在下降沿,触发(N-1)/2翻转和0翻转,然后将clk_p和clk_n做或逻辑运算即可得到占空比50%的计数分频信号。从以上可以看出,占空比50%的奇数分频只是在占空比非50%的奇数分频的基础上多做了一个逻辑运算。

小数分频:目前小数分频使用较多的方法是双模前置分频法,基本原理是在小数分频的两侧寻找相近的分频去插入,营造在一定的源时钟周期走过与小数分频相当的的时钟周期。但是往往分频的时序波形比较乱,占空比几乎达不到50%,效果差强人意,究其根本原因是信号只在源时钟的边沿触发。

半整数分频:半整数分频是小数分频的特殊情况,之所以会拎出来单独讲,是因为根据小数分频的双模前置法做出来的波形时序较差。如果需要得50%的半整数分频怎么办? 首先做出两个上升沿和下降沿二分频信号,通过在半整数两边寻找相邻的的奇数和偶数(决定信号电平周期数),然后做逻辑运算即可以得到占空比50%的半整数分频。

状态机分频:可以实现分频的方式之一,对于简单的分频器可以采用状态机来实现,大部分情况状态机用来处理较为复杂的情况与问题,在分频电路里有大材小用的感觉,电路分频时可以采用更简单的计数器代替状态机的状态转换。

不定期检查、补充、纠错,欢迎随时交流纠错

最后修改日期:2023.5.10

软件版本:

- 仿真软件:Modelsim 10.6c

- 时序绘制软件:TimeGen 3.2

- 描述语言:verilog