timer >= 32'd89_999_999 ) && (timer[1:0] == 2'b00 ) ) ? 4'b0000 :

( led_mode[3] && (timer >= 32'd89_999_999 ) ) ? 4'b1111 :

// 12.5%

( led_mode[3] && (timer >= 32'd69_999_999 ) && (timer[2:0] == 3'b000) ) ? 4'b0000 :

( led_mode[3] && (timer >= 32'd69_999_999 ) ) ? 4'b1111 :

// 6.25%

( led_mode[3] && (timer >= 32'd49_999_999 ) && (timer[3:0] == 4'b000) ) ? 4'b0000 :

( led_mode[3] && (timer >= 32'd49_999_999 ) ) ? 4'b1111 :

// 3.12%

( led_mode[3] && (timer >= 32'd29_999_999 ) && (timer[4:0] == 5'b000) ) ? 4'b0000 :

( led_mode[3] && (timer >= 32'd29_999_999 ) ) ? 4'b1111 :

// 1.56%

( led_mode[3] && (timer >= 32'd9_999_999 ) && (timer[5:0] == 6'b000) ) ? 4'b0000 :

( led_mode[3] && (timer >= 32'd9_999_999 ) ) ? 4'b1111 :

// 0%

( led_mode[3] ) ? 4'b1111 : 4'b1111 ;

endmodule

上述方式是一种实现呼吸灯占空比调节的思路,

当然,并不是唯一的方法,这里再提供一种其他的设计思路,

有兴趣的读者可以研究一下如何用这种方式对呼吸灯模式的控制进行复现:

https://blog.csdn.net/spx1164376416/article/details/124935001?ops_request_misc=&request_id=&biz_id=102&utm_term=PWM verilog&utm_medium=distribute.pc_search_result.none-task-blog-2~

至此,Control Unit模块的设计思路就介绍完了,

在下面的第五章中,我们将演示系统在FPGA开发板上的实际运行视频

5. FPGA验证

本项目所用开发板型号:XC7A35T-2FGG484I

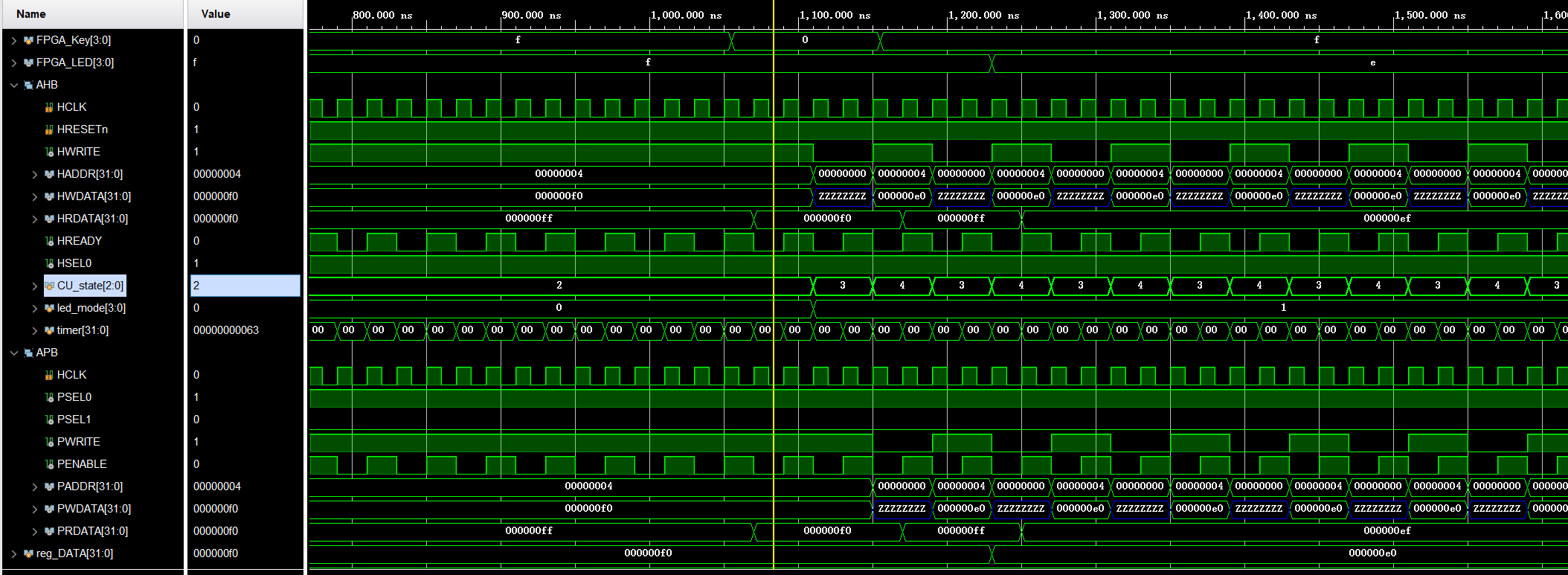

5.1 动态仿真验证

上板运行系统之前,先编写Testbench仿真观察一下波形:

-

上电后CU对GPIO寄存器进行配置(CU模块状态机0->1->2)

-

同时按下四个按键(FPGA_key[3:0]=4'd0),进入流水灯模式,(CU模块状态机3<->4)

-

按下key1(FPGA_key[3:0]=4'dd),进入加速流水灯模式

-

其余几个模式同理,这里不一一展示了,附Testbench代码:

点击查看代码

module tb_SoC_top ();

reg HCLK ;

reg HRESETn ;

reg [3:0] FPGA_Key;

wire [3:0] FPGA_LED;

SoC_top u_test(

.HCLK (HCLK ),

.HRESETn (HRESETn ),

.FPGA_Key(FPGA_Key),

.FPGA_LED(FPGA_LED)

);

initial begin

forever #10 HCLK = !HCLK; //50MHz

end

initial begin

HCLK = 0;

HRESETn = 0;

FPGA_Key = 4'b1111;

#55

HRESETn = 1;

#1000

FPGA_Key = 4'b0000; //key1~4 pressed

#100

FPGA_Key = 4'b1111; //key release

#1000

FPGA_Key = 4'b1110; //key1 pressed

#100

FPGA_Key = 4'b1111; //key release

#1000

FPGA_Key = 4'b1101; //key2 pressed

#100

FPGA_Key = 4'b1111; //key release

#1000

FPGA_Key = 4'b1011; //key3 pressed

#100

FPGA_Key = 4'b1111; //key release

#1000

FPGA_Key = 4'b1110; //key3 pressed

#100

FPGA_Key = 4'b1111; //key release

end

endmodule

5.2 FPGA开发板实速运行

上板验证视频:https://www.bilibili.com/video/BV1EM4y1U7QP/?vd_source=b96e62cf611b2bbbbacda9f1c4d9a394

本项目所用开发板型号:XC7A35T-2FGG484I

开发板资源使用情况如图: