_1状态之间的转换波形:

其他几段状态转化处的波形也是同理,在此不在一一标注解释了,具体如下:

MARCH_1状态和MARCH_2状态之间的波形:

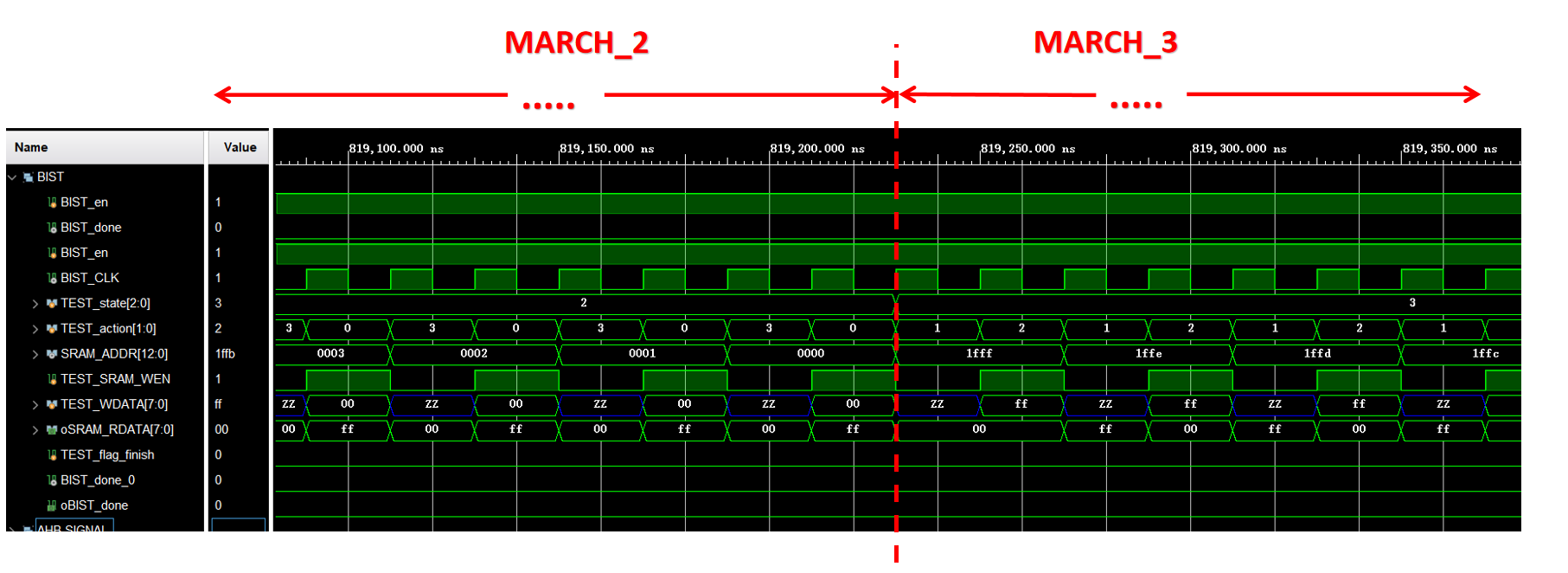

MARCH_2状态和MARCH_3状态之间的波形:

MARCH_3状态和MARCH_4状态之间的波形:

MARCH_4状态最后一段波形:

完成MARCH_4后,BIST_done被拉高,代表BIST结束。

以上,就是关于AHB-SRAN的BIST模式下的逻辑仿真解读。

最后附上两种工作模式下的Testbench:

点击查看代码

`timescale 1ns / 1ps

module sram_tb #(

//HRESP

parameter OKAY = 2'b00 ,

parameter ERROR = 2'b01 ,

parameter SPLIT = 2'b10 ,

parameter RETRY = 2'b11 ,

//HTRANS

parameter IDLE = 2'b00 ,

parameter BUSY = 2'b01 ,

parameter SEQ = 2'b10 ,

parameter NONSEQ = 2'b11 ,

//HSIZE

parameter BYTE = 3'b000 ,

parameter WORD = 3'b001 ,

parameter DWORD = 3'b010 ,

//HBURST

parameter SINGLE = 3'b000 ,

parameter INCR = 3'b001 ,

parameter WRAP4 = 3'b010 ,

parameter INCR4 = 3'b011 ,

parameter WARP8 = 3'b100 ,

parameter INCR8 = 3'b101 ,

parameter WARP16 = 3'b110 ,

parameter INCR16 = 3'b111

)();

// input output declaration

reg HCLK;

reg HRESETn;

reg HSEL ;

reg [1:0] HTRANS;

reg [2:0] HBURST;

reg [2:0] HSIZE ;

reg HWRITE;

reg [15:0] HADDR ;

reg [31:0] HWDATA;

wire HREADY;

wire [1:0] HRESP ;

wire [31:0] HRDATA;

// BIST IO

reg BIST_en;

wire BIST_done;

wire BIST_fail;

// top module instantion

sram_top u_test(

.HCLK (HCLK ),

.HRESETn(HRESETn),

.HSEL (HSEL ),

.HTRANS (HTRANS ),

.HBURST (HBURST ),

.HSIZE (HSIZE ),

.HWRITE (HWRITE ),

.HADDR (HADDR ),

.HWDATA (HWDATA ),

.HREADY (HREADY ),

.HRESP (HRESP ),

.HRDATA (HRDATA ),

.BIST_en (BIST_en ),

.BIST_done(BIST_done),

.BIST_fail(BIST_fail)

);

// Excitation Vector Generation

initial begin

forever #10 HCLK = ~HCLK; //50Mhz

end

initial begin

HCLK = 0;

HRESETn = 0;

// Choose BIST Mode/ FUNC Mode to run simulation

/*――――――――――――――――――――――――――――――――――――――――――――――――――――――――――――――――――――――――*\

/ Testbench for BIST Mode \

\*――――――――――――――――――――――――――――――――――――――――――――――――――――――――――――――――――――――――*/

/*

BIST_en = 1;

end

*/

/*――――――――――――――――――――――――――――――――――――――――――――――――――――――――――――――――――――――――*\

/ Testbench for FUNC Mode \

\*――――――――――――――――――――――――――――――――――――――――――――――――――――――――――――――――――――――――*/

HRESETn = 0;

BIST_en = 0;

HSEL = 0;

HTRANS = 3'b111;

HBURST = 2'b11;

HSIZE = 3'b111;

HWRITE = 1'b0;

HADDR = 16'h0000; //HADDR[1:0] have to be 2'b00 ( 4n )

HWDATA = 32'h0;

#65 HRESETn = 1;

//-------------------------WRITE MEM---------------

#20

// write control0

HSEL = 1;

HTRANS = NONSEQ;

HBURST = SINGLE;

HSIZE = WORD;

HWRITE = 1'b1;

HADDR = 16'h0000;

#20

// data0 → mem(0x0000)

HWDATA = 32'h11223344;

// write control 1

HWRITE = 1'b1;

HADDR = 16'h0004;

#20

// data1 → mem(0x0004)

HWDATA = 32'h55667788;

// write control 2

HWRITE = 1'b1;

HADDR = 16'h0008;

#20

// data2 → mem(0x0008)

HWDATA = 32'h99AABBCC;

//// write control 3

//HWRITE = 1'b1;

//HADDR = 16'h000C;

#20

// data3 → mem(0x000C)

HWDATA = 32'hAAAAAAAA;

// write control 4

HWRITE = 1'b1;

HADDR = 16'h0010;

#20

// data4 → mem(0x0010)

HWDATA = 32'hBBBBBBBB;

// write control 5

HWRITE = 1'b1;

HADDR = 16'h0014;

#20

// data5 → mem(0x0014)

HWDATA = 32'hCCCCCCCC;

// write control 6

HWRITE = 1'b1;

HADDR = 16'h8000;

#20

// data6 → mem(0x8000)

HWDATA = 32'hDDDDDDDD;

// write control 7

HWRITE = 1'b1;

HADDR = 16'h8004;

#20

// data7 → mem(0x8004)

HWDATA = 32'hEEEEEEEE;

// write control 8

HWRITE = 1'b1;

HADDR = 16'h8008;

#20

// data8 → mem(0x8008)

HWDATA = 32'hFFFFFFFF;

// read control 0

HWRITE = 1'b0;

HADDR = 16'h0000;

//--------------READ MEM----------------

#