|

st_n <= 0;

#200

rst_n <= 1;

end

reg Send_en;

reg [7:0]Data_send;

wire Read_en;

wire [7:0]Data_recive;

wire Spi_clk;

wire Spi_mosi;

wire Spi_miso;

wire Cs_output;

SPI_Interface

# (

.Value_divide (4))

SPI_inst

(

//-----------------内部接口------------------

.Clk (clk_50m),

.Rst_n (rst_n),

.CPOL (1),

.CPHA (0),

.CS_input (1),

.Send_en (Send_en),

.Data_send (Data_send),

.Read_en (Read_en),

.Data_recive (Data_recive),

//------------------外部接口------------------

.Spi_clk (Spi_clk),

.Spi_mosi (Spi_mosi),

.Spi_miso (Spi_miso),

.Cs_output (Cs_output)

);

assign Spi_miso = Spi_mosi;

initial begin

Send_en <= 0;

Data_send <= 0;

#400;

Send_en <= 1;

Data_send <= 8'haf;

#20

Send_en <= 0;

#800;

Send_en <= 1;

Data_send <= 8'h55;

#20

Send_en <= 0;

end

endmodule

2、仿真结果

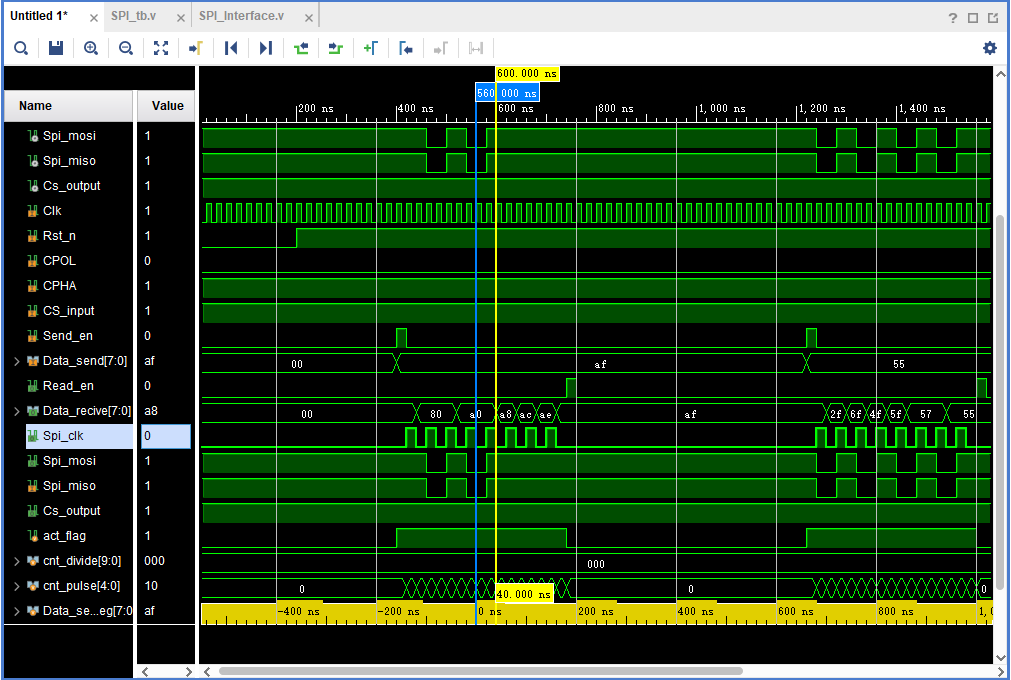

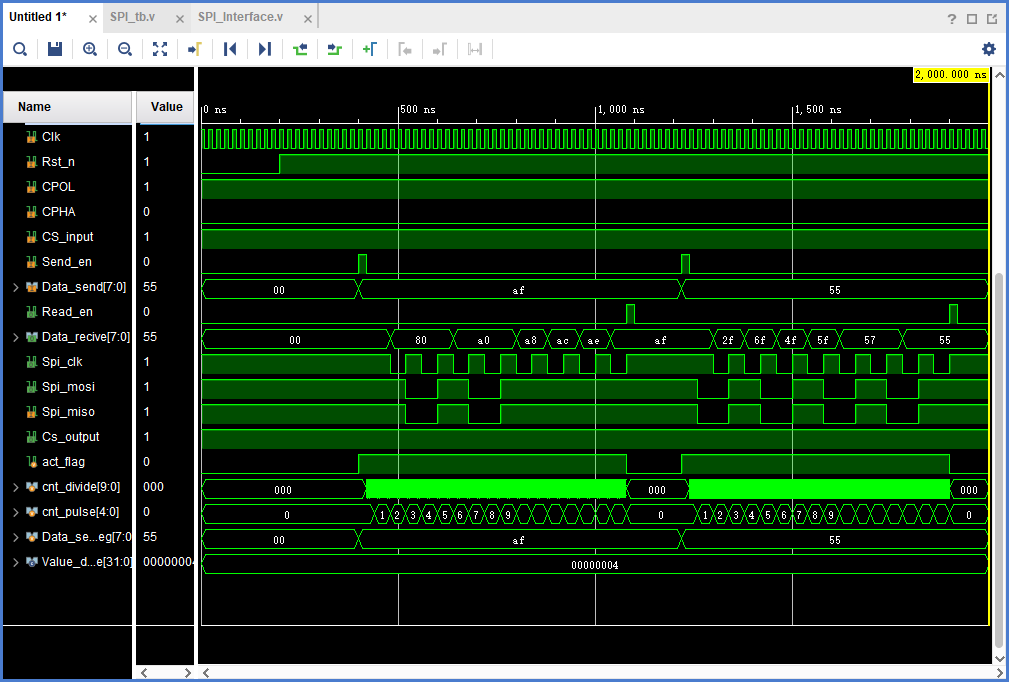

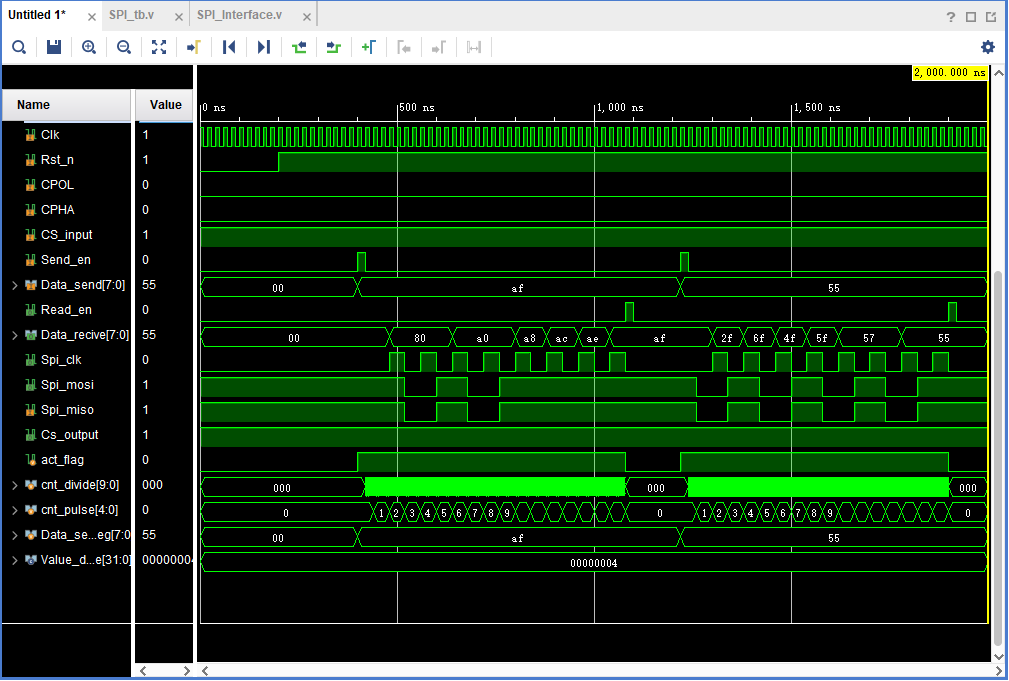

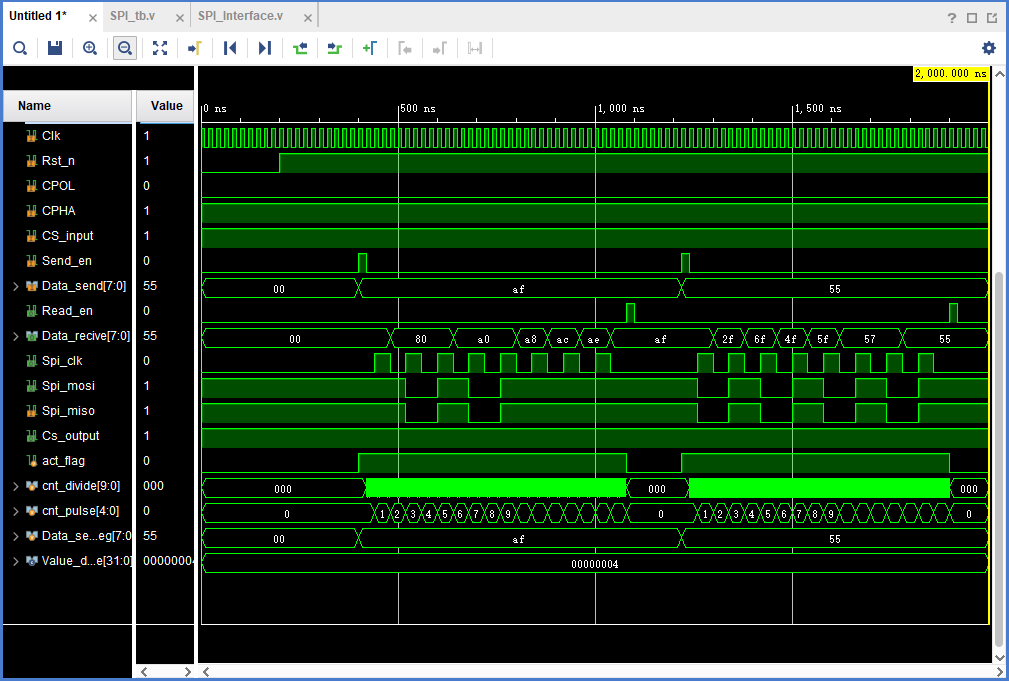

两倍分频:

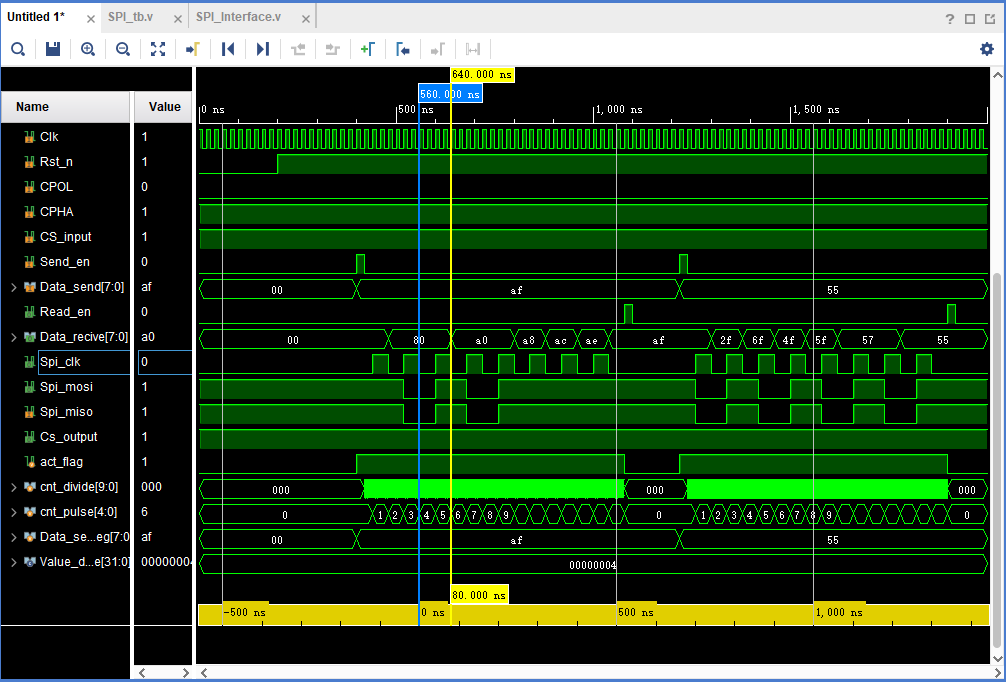

四倍分频:

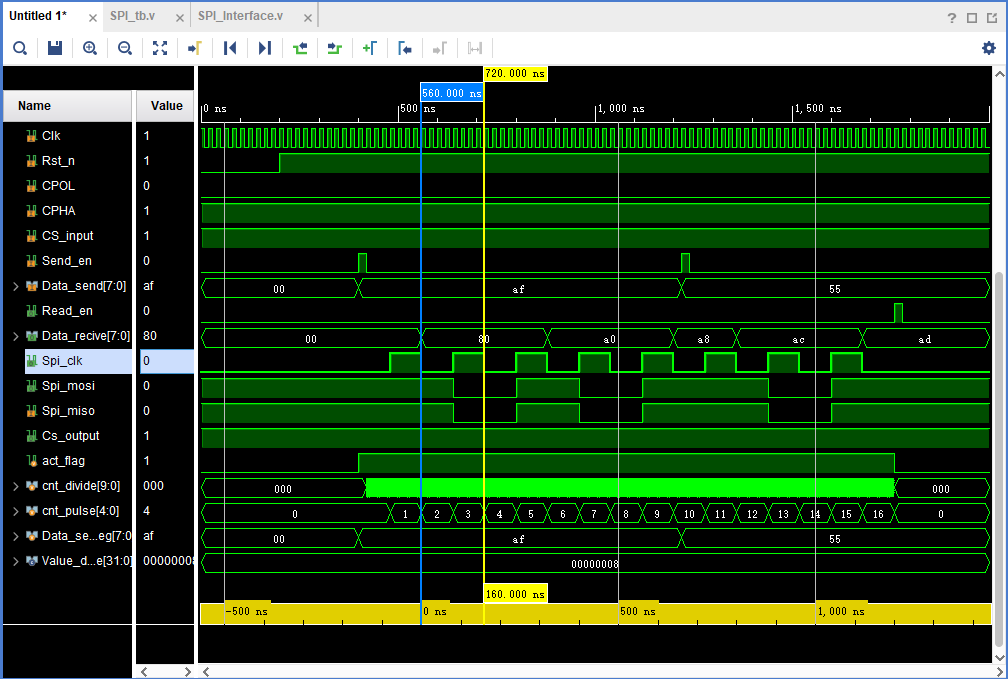

八倍分频:

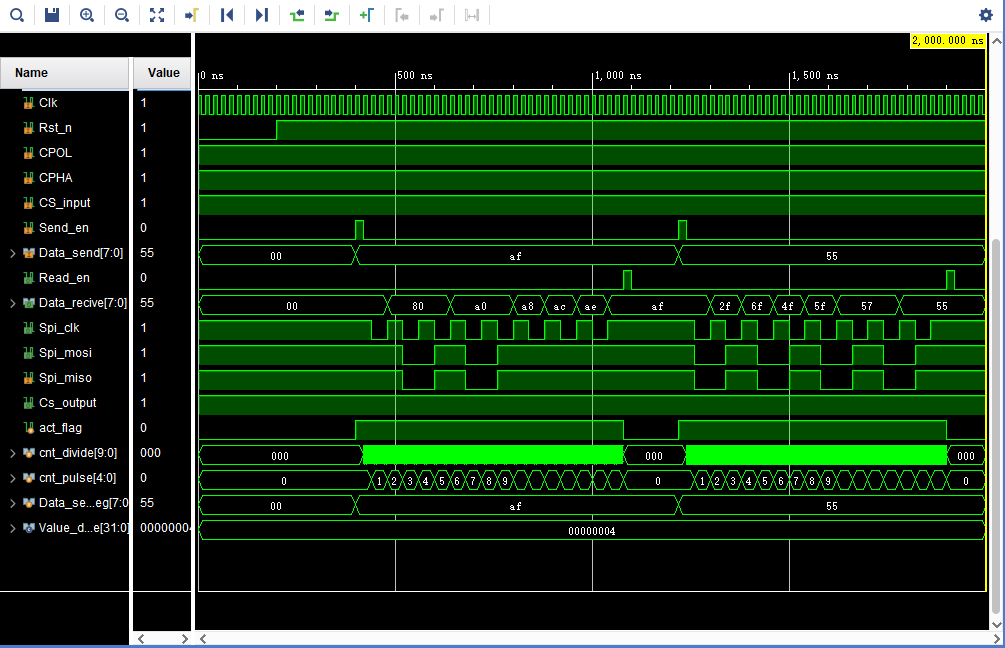

CPOL=1、CPHA=1;

CPOL=1、CPHA=0;

CPOL=0、CPHA=0;

CPOL=0、CPHA=1;

结论:仿真实验初步成功,能够满足SPI通信的基本要求。

|