|

同步标志,在为高期间会复位单像素控制模块

ila_0 ila_0_inst (

.clk(Clk), // input wire clk

.probe0(ram_output_addr), // input wire [3:0] probe0

.probe1(ram_output_data), // input wire [23:0] probe1

.probe2(Data_valid), // input wire [0:0] probe2

.probe3(Data_out) // input wire [0:0] probe3

);

vio_0 vio_0_inst (

.clk(Clk), // input wire clk

.probe_out0(ram_input_addr), // output wire [3 : 0] probe_out0

.probe_out1(ram_input_data), // output wire [23 : 0] probe_out1

.probe_out2(ram_input_en) // output wire [0 : 0] probe_out2

);

blk_mem_gen_0 blk_mem_gen_0_inst (

.clka(Clk), // input wire clka

.wea(ram_input_en), // input wire [0 : 0] wea

.addra(ram_input_addr), // input wire [3 : 0] addra

.dina(ram_input_data), // input wire [23 : 0] dina

.clkb(Clk), // input wire clkb

.addrb(ram_output_addr), // input wire [3 : 0] addrb

.doutb(ram_output_data) // output wire [23 : 0] doutb

);

WS2812B_controller WS2812B_controller_inst(

.Clk(Clk),

.Rst_n(~act_60us & Rst_n),

.Disp_Data(ram_output_data),

.Data_valid(Data_valid),

.Send_done(Send_done),

.Data_out(Data_out_t)

);

always @(posedge Clk or posedge Rst_n) begin

if(Rst_n == 0)

ram_output_addr <= 0;

else if(cnt_60us == CNT_60US - 1 )

ram_output_addr <= 0;

else if(Send_done == 1 & ~act_60us)

ram_output_addr <= ram_output_addr + 1'b1;

else

ram_output_addr <= ram_output_addr;

end

always @(posedge Clk) Send_done_r <= Send_done;

always @(posedge Clk or posedge Rst_n) begin

if(Rst_n == 0)

Data_valid <= 0;

else if((Send_done_r == 1 & ~act_60us)|cnt_60us == CNT_60US - 1)

Data_valid <= 1;

else

Data_valid <= 0;

end

always @(posedge Clk or posedge Rst_n) begin

if(Rst_n == 0)

act_60us <= 0;

else if(ram_output_addr == 4'hf & Send_done == 1)

act_60us <= 1;

else if(cnt_60us == CNT_60US - 1)

act_60us <= 0;

else

act_60us <= act_60us;

end

always @(posedge Clk or posedge Rst_n) begin

if(Rst_n == 0)

cnt_60us <= 0;

else if(cnt_60us == CNT_60US - 1)

cnt_60us <= 0;

else if(act_60us)

cnt_60us <= cnt_60us + 1'b1;

else

cnt_60us <= 0;

end

assign Data_out = (act_60us)? 0:Data_out_t;

endmodule

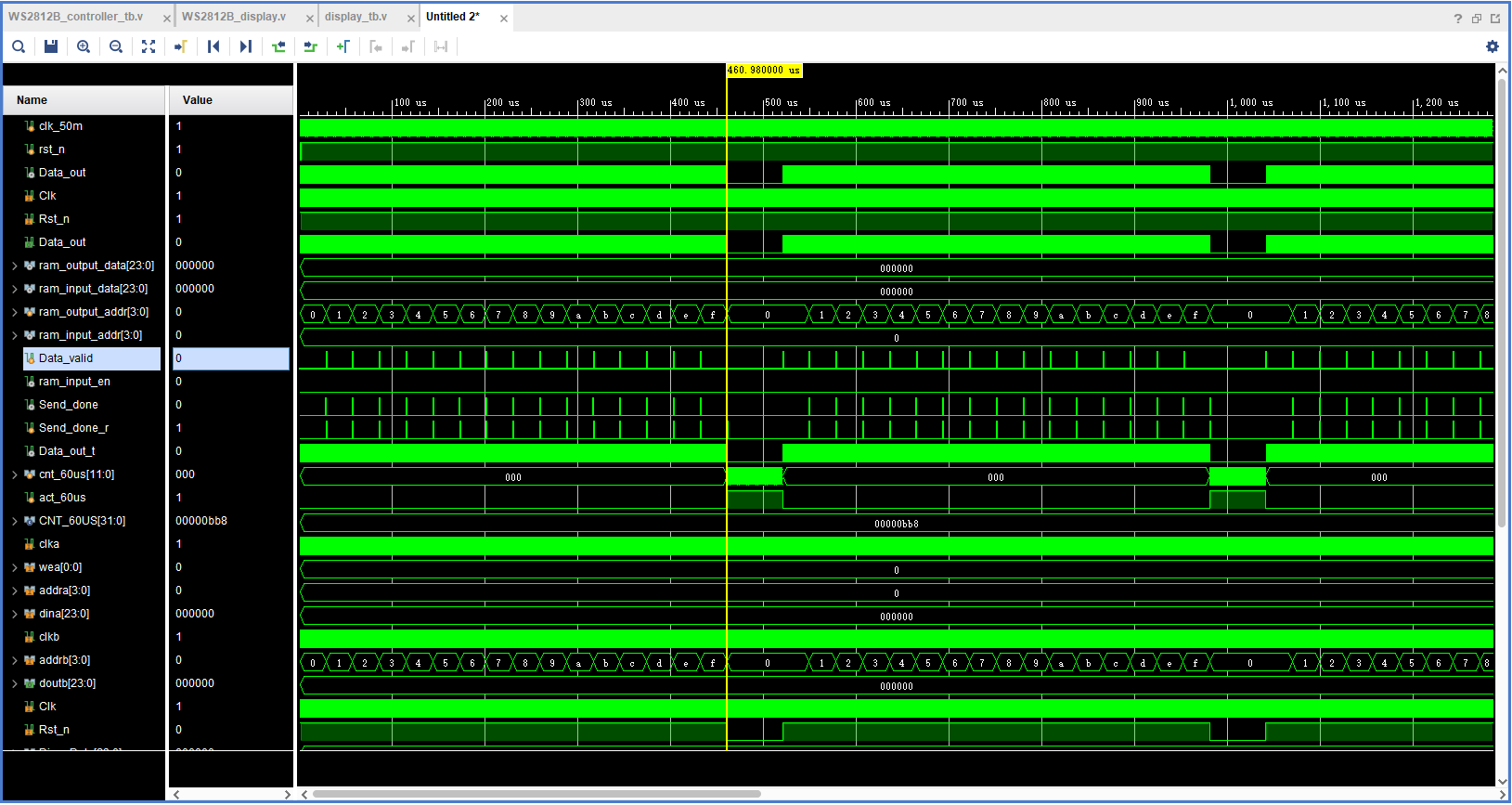

4、多像素显示模块仿真

仿真文件

`timescale 1ns / 1ps

module display_tb();

reg clk_50m;

initial clk_50m <= 1;

always #10 clk_50m <= ~clk_50m;

reg rst_n;

initial begin

rst_n <= 0;

#200

rst_n <= 1;

end

wire Data_out;

WS2812B_display WS2812B_display_inst(

.Clk(clk_50m),

.Rst_n(rst_n),

.Data_out(Data_out)

);

endmodule

仿真结果

结论:模块能够正确给出Data_valid和send_done信号,且60us的帧同步信号也能正确的给出。仿真通过

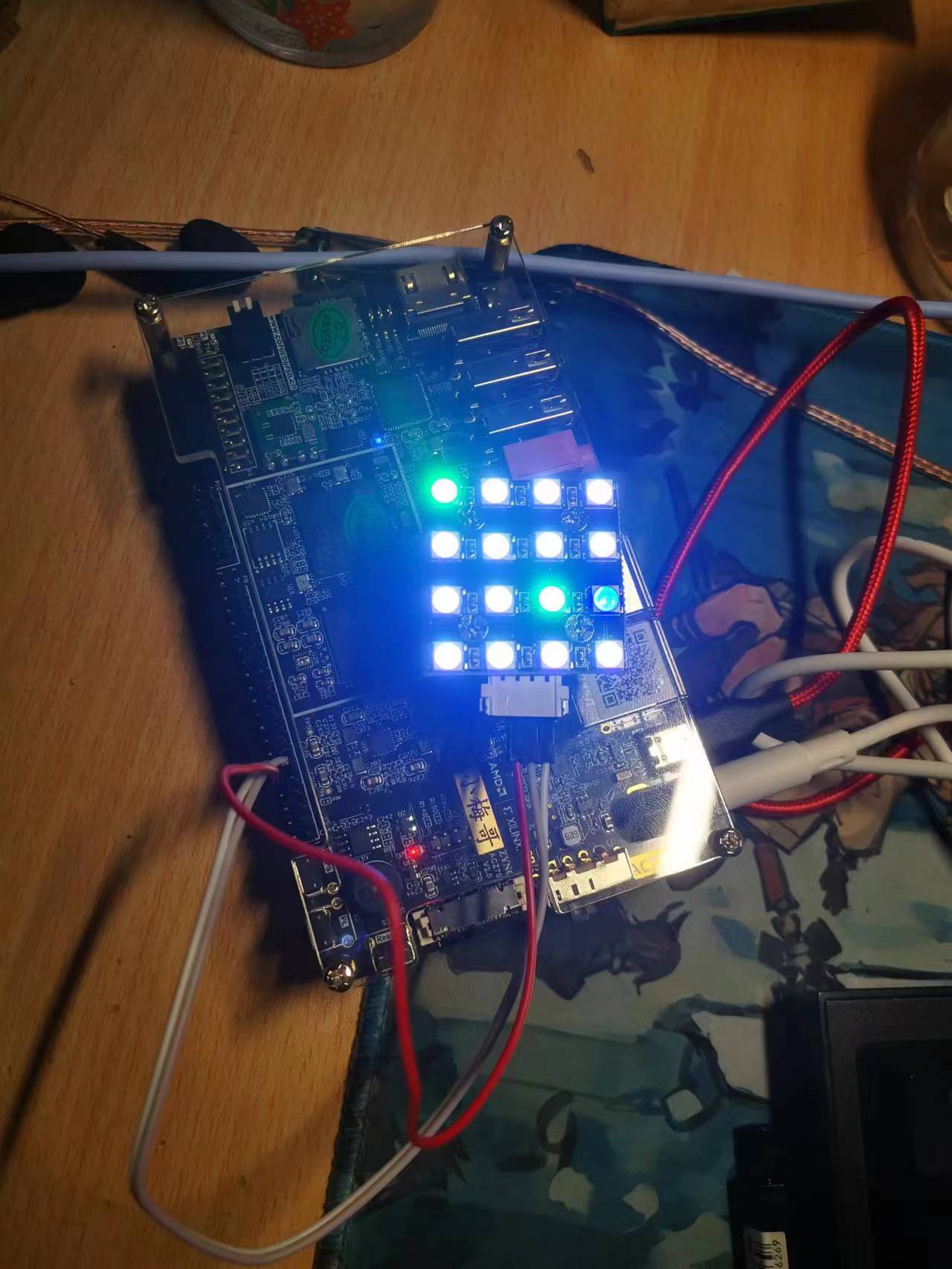

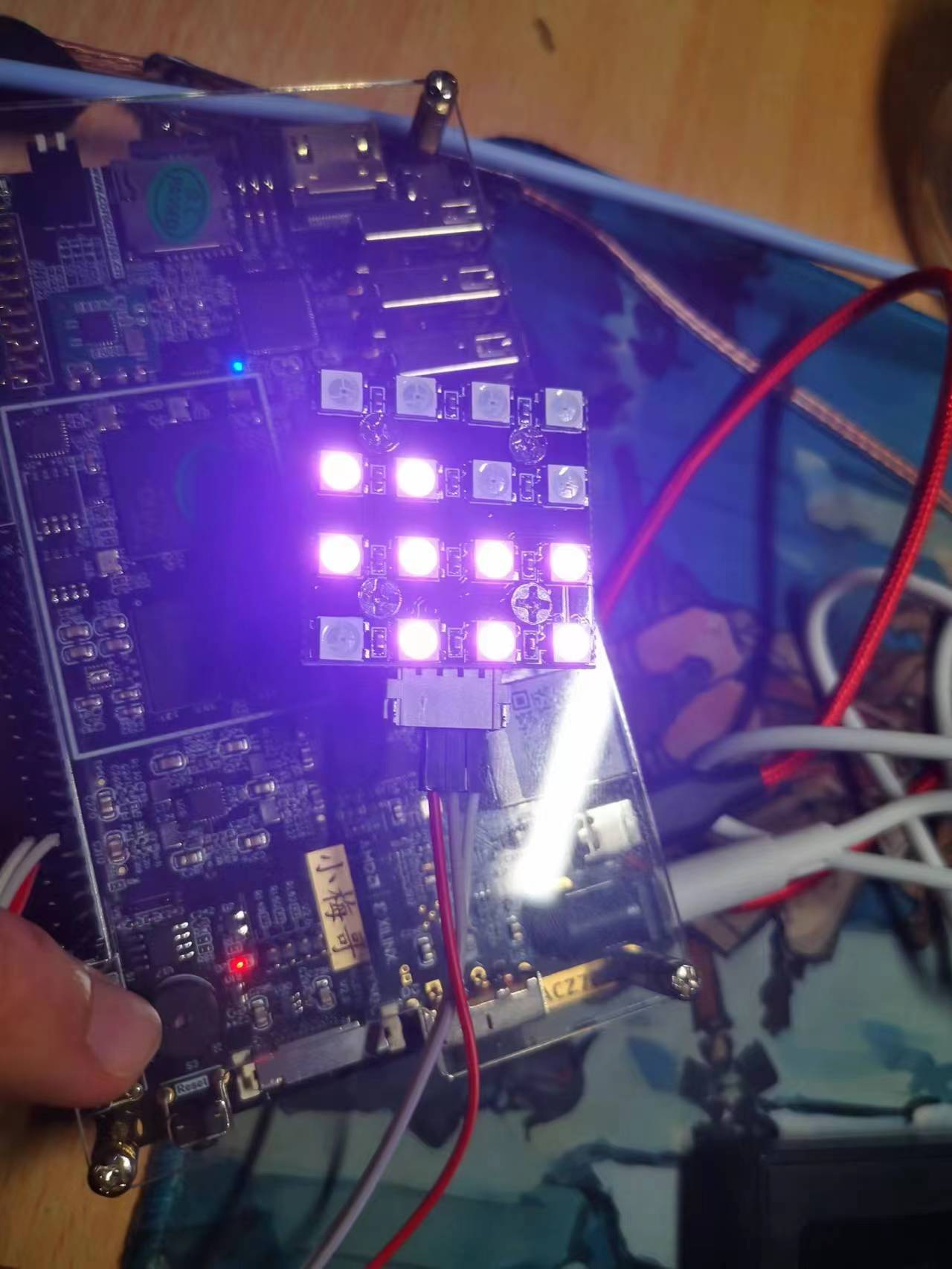

二、上板验证

将程序烧入芯片中,通过VIO控制写入RAM的数据可以改变RGB的状态。

该模块能够正常的改变每个RGB的状态,该模块初步验证可行。

|