nd_en; //8位数据的发送使能

wire tx_done; //8位数据的发送结束

reg [ 4:0] rounds; //需要发送的次数

uart_byte_tx //串口8位发送模块

# ( .TX_BAUD (9600), //波特率

.CLK_FQC (50_000_000)) //模块的时钟频率

uart_byte_tx_inst

(

.Data (data_reg),

.Send_en (send_en),

.Clk (Clk),

.Rst_n (Rst_n),

.Uart_Tx (Uart_Tx),

.Tx_done (tx_done)

);

always @(posedge Clk or negedge Rst_n) begin //数据寄存

if(Rst_n == 0)

bytes_data_reg <= 0;

else if(Send_bytes_en)

bytes_data_reg <= Bytes_data;

else

bytes_data_reg <= bytes_data_reg;

end

always @(posedge Clk or negedge Rst_n) begin //状态机

if(Rst_n == 0) begin

state <= 0;

data_reg <= 0;

send_en <= 0;

Tx_bytes_done <= 0;

end

else case(state)

0: begin

if(Send_bytes_en)

state <= 3'b1;

else begin

state <= 0;

data_reg <= 0;

send_en <= 0;

Tx_bytes_done <= 0;

end

end

1: begin

if(rounds == ROUNDS) begin

Tx_bytes_done <= 1'b1;

state <= 0;

end

else begin

data_reg <= bytes_data_reg[7:0];

send_en <= 1'b1;

state <= 3'd2;

end

end

2: begin

send_en <= 0;

if(tx_done) begin

bytes_data_reg <= bytes_data_reg >> 8;

state <= 3'd1;

end

else

state <= 3'd2;

end

endcase

end

always @(posedge Clk or negedge Rst_n) begin //发送次数计数

if(Rst_n == 0)

rounds <= 0;

else if(rounds == ROUNDS & state == 1)

rounds <= 0;

else if(tx_done)

rounds <= rounds + 1'b1;

end

endmodule

4、仿真验证

(1)仿真激励

`timescale 1ns / 1ps

module uart_bytes_tx_tb();

reg Clk;

reg Rst_n;

reg Send_bytes_en;

reg [63:0]Bytes_data;

wire Tx_bytes_done;

wire Uart_Tx;

uart_bytes_tx_3

# ( .DATA_WIDTH (64))

uart_bytes_tx_inst

(

.Clk (Clk),

.Rst_n (Rst_n),

.Bytes_data (Bytes_data),

.Send_bytes_en (Send_bytes_en),

.Tx_bytes_done (Tx_bytes_done),

.Uart_Tx (Uart_Tx)

);

defparam uart_bytes_tx_inst.uart_byte_tx_inst.BAUD_CNT = 10;

initial Clk <= 1'b1;

always #10 Clk <= ~Clk;

initial begin

Rst_n <= 0;

Bytes_data <= 0;

Send_bytes_en <= 0;

#200

Rst_n <= 1'b1;

#20

Bytes_data <= 64'h0123456789abcdef;

Send_bytes_en <= 1'b1;

#20

Send_bytes_en <= 0;

#20000

Bytes_data <= 64'hfedcba9876543210;

Send_bytes_en <= 1'b1;

#20

Send_bytes_en <= 0;

@(posedge Tx_bytes_done)

#100

$stop;

end

endmodule

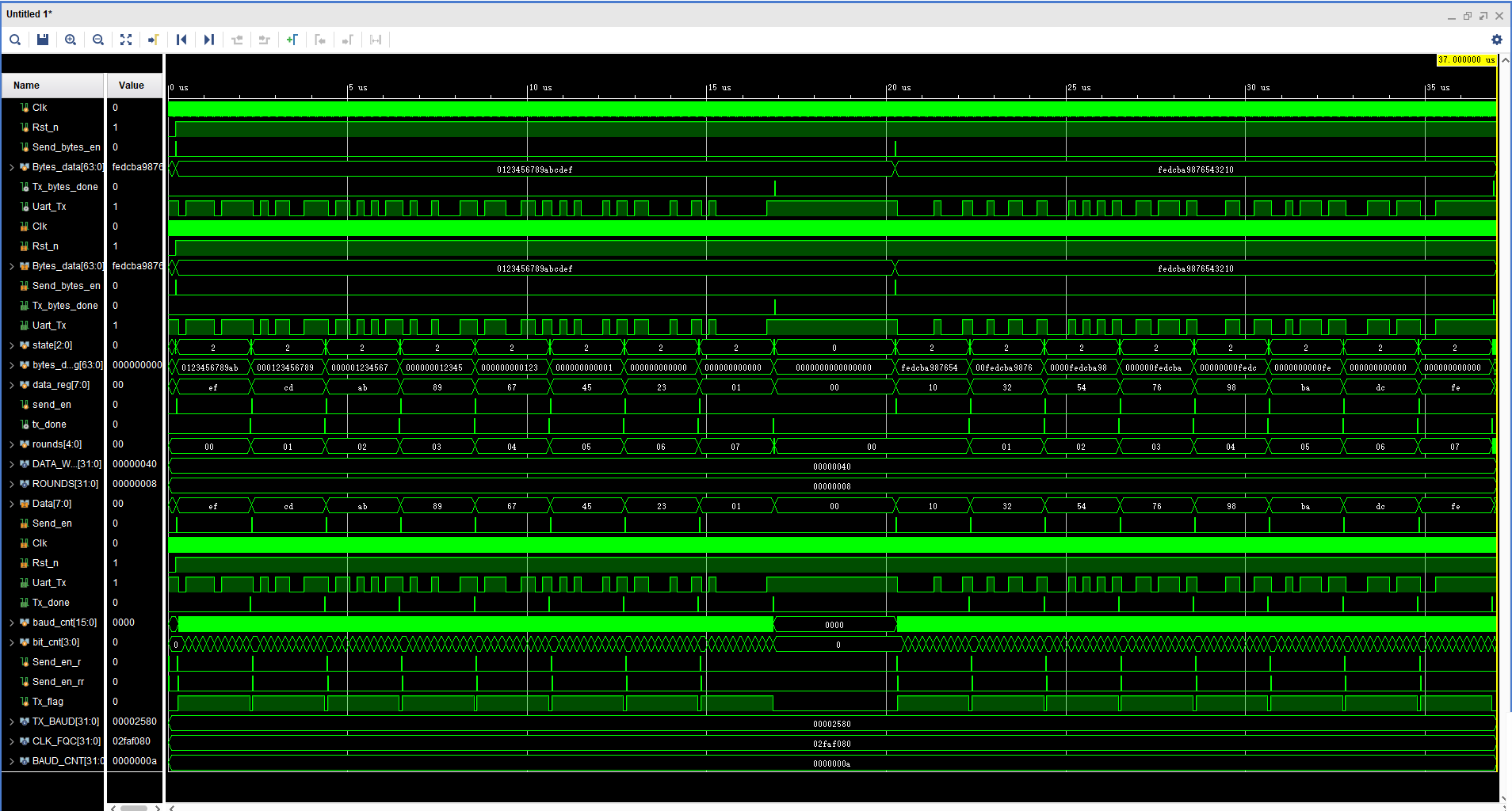

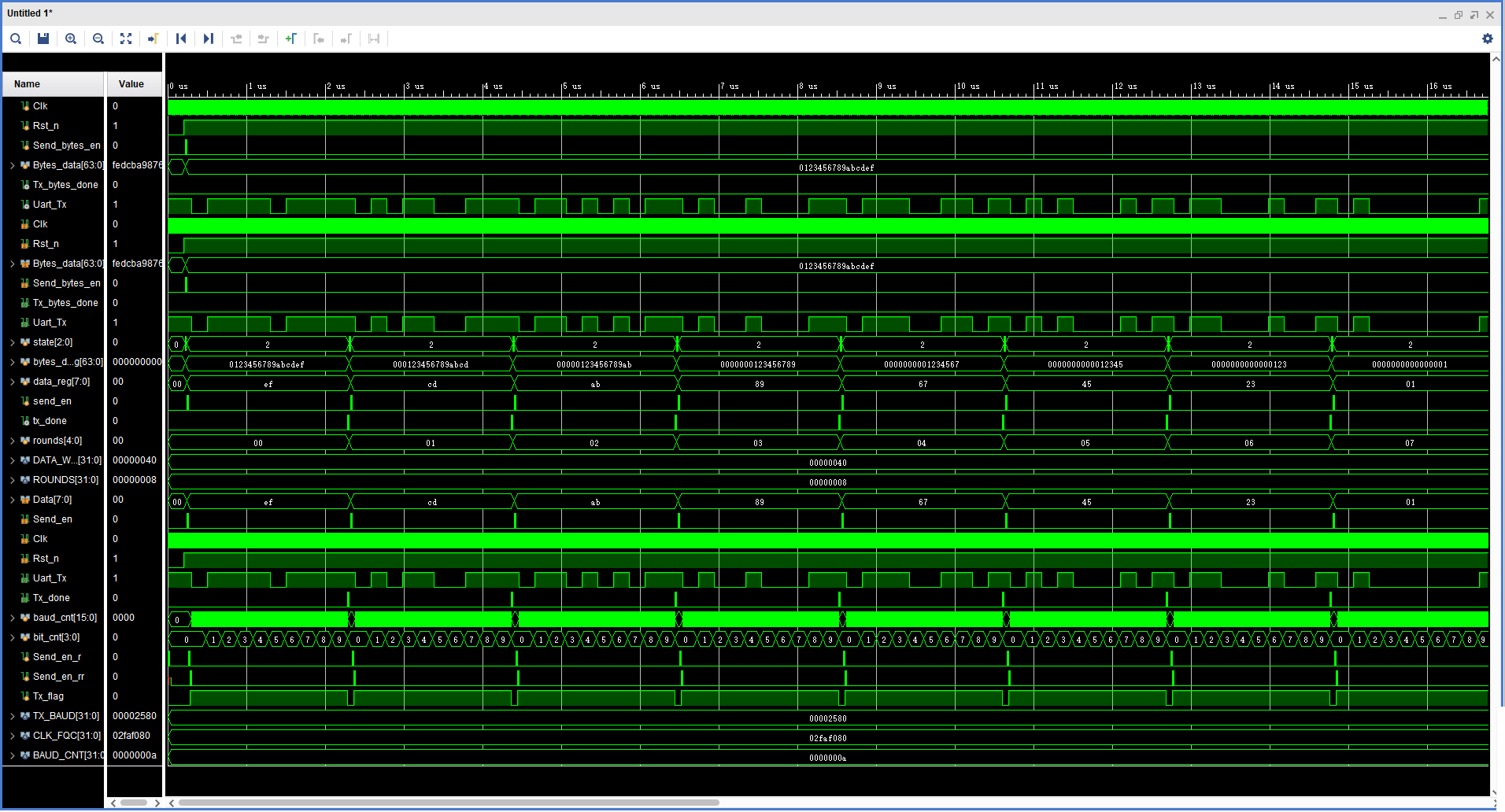

(2)仿真波形

第一轮发送:

两轮发送: