row1_col1;

row2_col2 <= line2_data;

row2_col1 <= row2_col2;

row2_col0 <= row2_col1;

end

else begin

row0_col2 <= row0_col2;

row0_col1 <= row0_col1;

row0_col0 <= row0_col0;

row1_col2 <= row1_col2;

row1_col1 <= row1_col1;

row1_col0 <= row1_col0;

row2_col2 <= row2_col2;

row2_col1 <= row2_col1;

row2_col0 <= row2_col0;

end

else begin

row0_col0 <= 'd0;

row0_col1 <= 'd0;

row0_col2 <= 'd0;

row1_col0 <= 'd0;

row1_col1 <= 'd0;

row1_col2 <= 'd0;

row2_col0 <= 'd0;

row2_col1 <= 'd0;

row2_col2 <= 'd0;

end

end

always @(posedge clk) begin

data_in_valid_dly1 <= data_in_valid;

data_in_valid_dly2 <= data_in_valid_dly1;

data_in_valid_dly3 <= data_in_valid_dly2;

data_in_hs_dly1 <= data_in_hs;

data_in_hs_dly2 <= data_in_hs_dly1;

data_in_hs_dly3 <= data_in_hs_dly2;

data_in_vs_dly1 <= data_in_vs;

data_in_vs_dly2 <= data_in_vs_dly1;

data_in_vs_dly3 <= data_in_vs_dly2;

end

assign data_out_valid = data_in_valid_dly3;

assign data_out_hs = data_in_hs_dly3;

assign data_out_vs = data_in_vs_dly3;

shift_register_2taps

#(

.DATA_WIDTH (DATA_WIDTH)

)

shift_register_2taps_inst

(

.clk (clk),

.shiftin (data_in),

.shiftin_valid (data_in_valid),

.shiftout (),

.taps1x (line1_data),

.taps0x (line0_data)

);

assign line2_data = data_in;

//----------------------------------------------------

// mask x mask y

//[-1,0,1] [ 1, 2, 1]

//[-2,0,2] [ 0, 0, 0]

//[-1,0,1] [-1,-2,-1]

//----------------------------------------------------

assign Gx_is_positive = (row0_col2 + row1_col2*2 + row2_col2) >=

(row0_col0 + row1_col0*2 + row2_col0);

assign Gy_is_positive = (row0_col0 + row0_col1*2 + row0_col2) >=

(row2_col0 + row2_col1*2 + row2_col2);

always @(posedge clk or posedge reset_p) begin

if(reset_p)

Gx_absolute <= 'd0;

else if(data_in_valid_dly1) begin

if(Gx_is_positive)

Gx_absolute <= (row0_col2 + row1_col2*2 + row2_col2) - (row0_col0 + row1_col0*2 + row2_col0);

else

Gx_absolute <= (row0_col0 + row1_col0*2 + row2_col0) - (row0_col2 + row1_col2*2 + row2_col2);

end

end

always @(posedge clk or posedge reset_p) begin

if(reset_p)

Gy_absolute <= 'd0;

else if(data_in_valid_dly1) begin

if(Gy_is_positive)

Gy_absolute <= (row0_col0 + row0_col1*2 + row0_col2) - (row2_col0 + row2_col1*2 + row2_col2);

else

Gy_absolute <= (row2_col0 + row2_col1*2 + row2_col2) - (row0_col0 + row0_col1*2 + row0_col2);

end

end

//----------------------------------------------------

//result

//----------------------------------------------------

always @(posedge clk or posedge reset_p) begin

if(reset_p)

data_out <= 1'b0;

else if(data_in_valid_dly2) begin

data_out <= ((Gx_absolute+Gy_absolute)>threshold) ? 1'b0 : 1'b1;

end

end

endmodule

5、仿真

仿真过程有复杂,调了许久,这里暂不写出。

6、上板验证

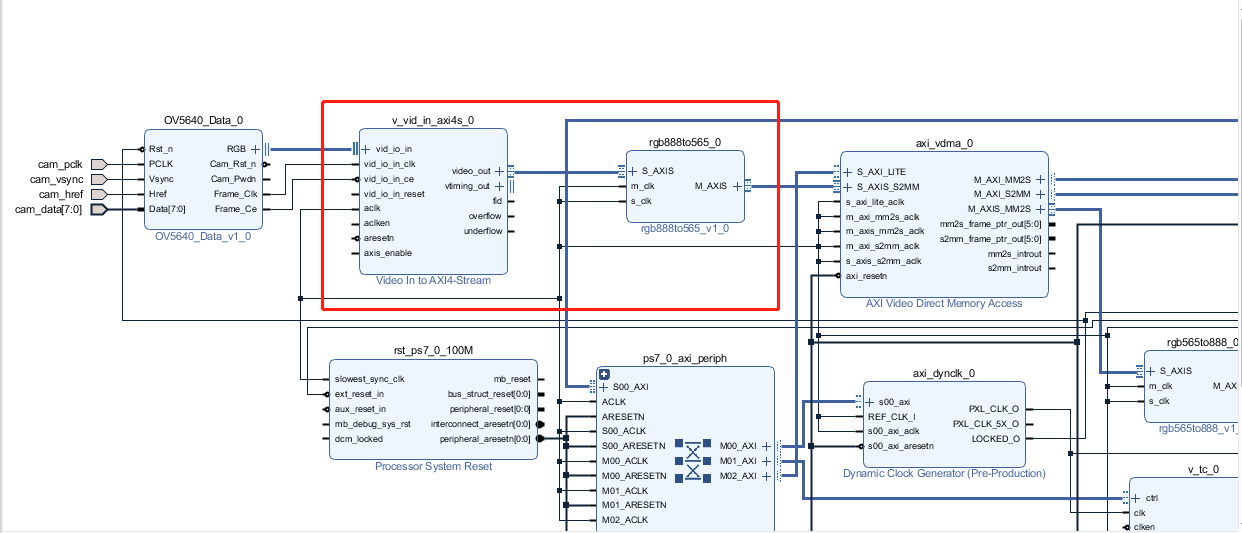

本次还是在小梅哥的OV5640_TFT这个工程的基础上进行修改,并将上面提到的模块打包成IP核,在block design里进行链接。

(1)删除红框内的模块

(2)修改OV5640_data_0 IP核

module OV5640_Data_v1_0(

Rst_n, //复位

PCLK, //像素时钟

Vsync, //场同步信号

Href, //行同步信号

Data, //数据

DataValid, //数据有效信号

DataPixel, //像素数据

Frame_Clk //时钟信号

);

input Rst_n; //复位

input PCLK; //像素时钟

input Vsync; //场同步信号

input Href; //行同步信号

input [7:0]Data; //数据

output DataValid; //数据有效信号

output [15:0]DataPixel; //像素数据

output Frame_Clk;//时钟信号

reg r_Vsync;

reg r_Href;

reg [7:0]r_