逻辑门延迟)。

2.2 建立时间与保持时间

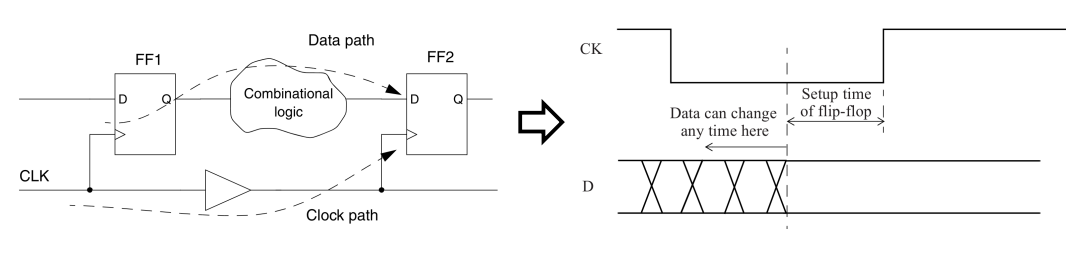

建立时间:在触发器的捕获沿到来之前,数据必须提前保持稳定的持续时间,以保证触发器可以顺利安全的取到数据。此参数可以用来约束数据路径上的最大时序。

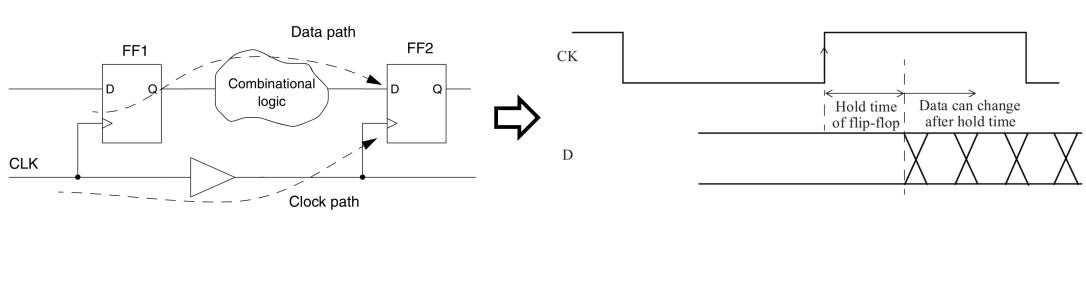

保持时间:在触发器的捕获沿到来之后数据必须保持稳定的持续时间。此参数可以用来约束数据路径的最小时序。

Tips:建立时间与保持时间对应的最大延时和最小延时不要记反了!

2.3 时序路径(Timing path)

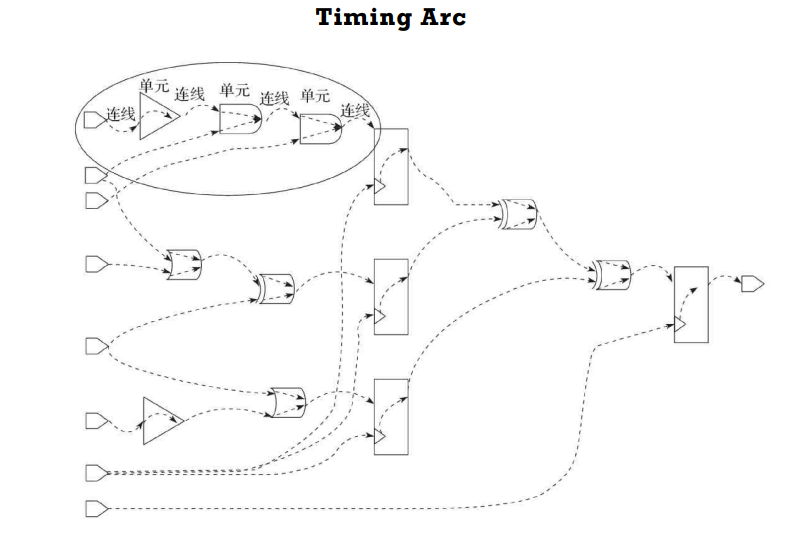

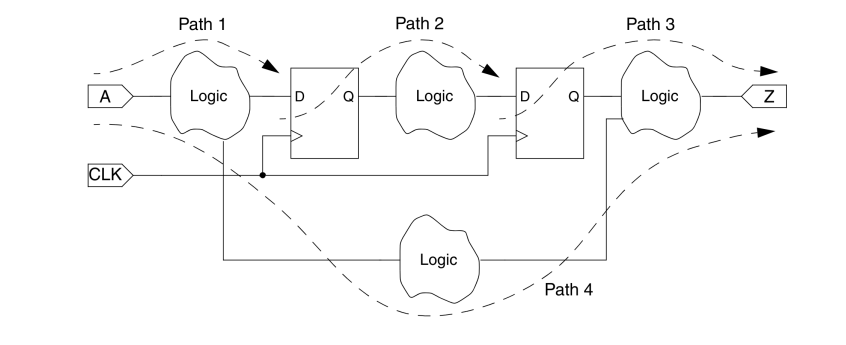

PrimeTime 进行时序分析的第一步是将设计分解为一组时序路径。每个时序路径都有一个起点和终点,起点和终点各有两种,起点包括 clock pin 和 input port,终点包括data input pin 和 output port,所以一共有四种时序路径。

2.4时钟域(Clock Domains)

大多数数字电路都是“全局异步,局部同步”的时序,但是所有的静态时序分析(STA)都是针对的同步电路。

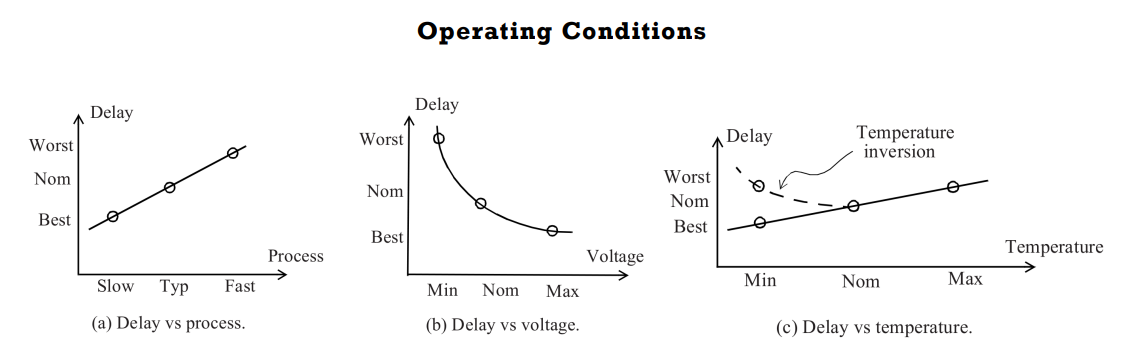

2.5 操作条件(Operating Conditions)和 PVT(Process Voltage Temperature)

由于半导体不同的工艺制成,不同的使用环境,对器件本身的延迟存在较大影响。所以在进行STA时一定要明确操作的环境和条件,主要包括工艺制程(Process)、电压(Voltage)、温度(Temperature)。在指定上述的条件之后,单元延时和互连线的延时也就根据上述条件进行计算分析。

工艺制程的模型主要分为3种:slow、typical、fast。其中 slow 和 fast都是极端的条件,对于稳健的设计,PVT(Process Voltage Temperature)都要在极端环境下测试通过。高温低压对应最坏的情况,低温高压对应最佳情况。

一般在最大延迟环境下检查建立时间,在最小延迟环境下检查保持时间。

三、标准单元工艺库

3.1 库文件概述

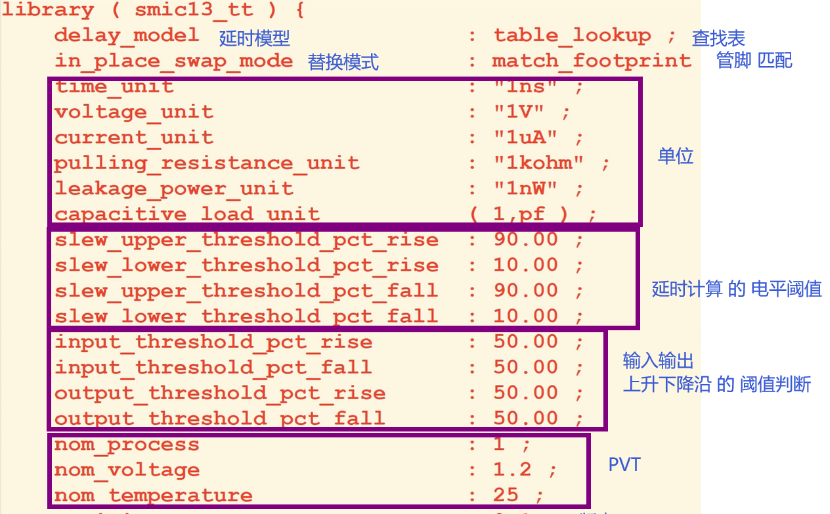

通过库文件可以读出单元的相关信息,如下图所示:

具体可以参考:静态时序分析(STA)―― 标准单元库

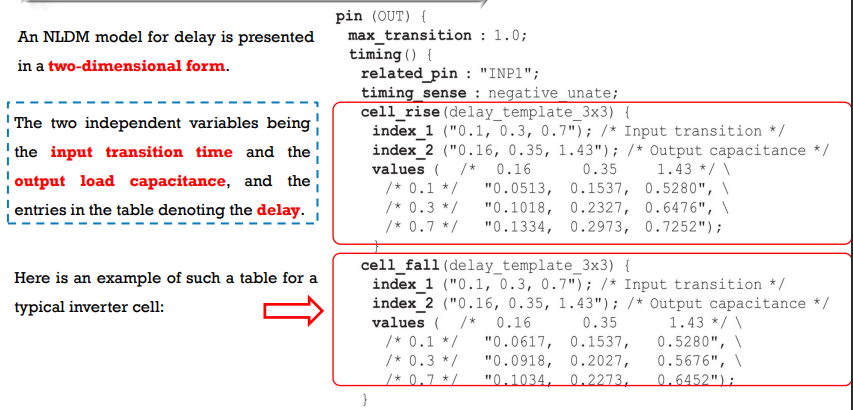

3.2 非线性延迟模型

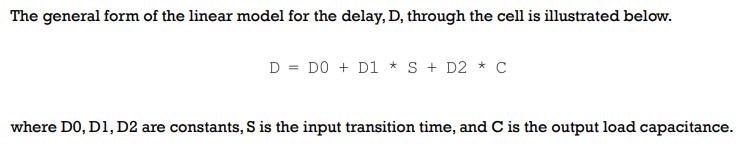

单元延迟取决于两个因素:输出负载电容和电平转换时间

1、输出负载,即输出端的电容负载的大小。容性负载越大,延迟越大。

2、输入端信号高低电平转换时间。大多数情况下,此参数越大,对应的延时也会越大。

根据电容负载和电平转换时间可以推导出线性延迟模型去预估模型的具体延迟。然而,线性模型在微小工艺半导体器件中并不是很精确,大都数用的是非线性模型。

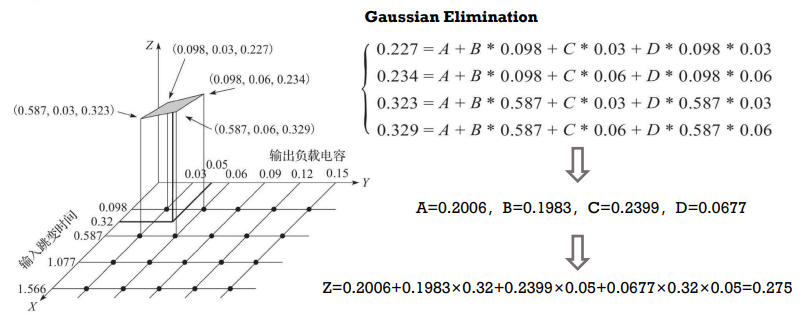

第一步:根据查表法得到对应的延时。

第二步:如果找不到对应的点,则根据相邻的四个点进行插值然后根据高斯消元法得到模型延时。

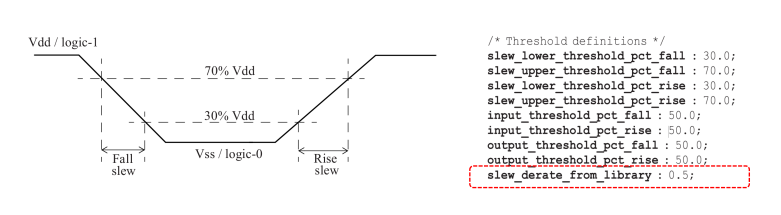

3.3 电平翻转阈值调整(slew_derate)

电平翻转阈值调整主要是应对一些实际工艺制程与工艺库的不同导致延迟差异的问题。例如工艺库单元阈值为10%―90%,而实际的工艺为30%―70%,阈值相当于下降了50%。为了解决这类问题,只需要slew_derate_from_library设置为0.5即可。如下图所示:

四、建立静态时序分析的环境

正确的约束对于分析STA结果很重要,只有准确指定设计环境,STA分析才能够识别出设计中的所有时序问题。STA的准备工作包括设置时钟、指定IO时序特性以及指定伪路径和多周期路径。

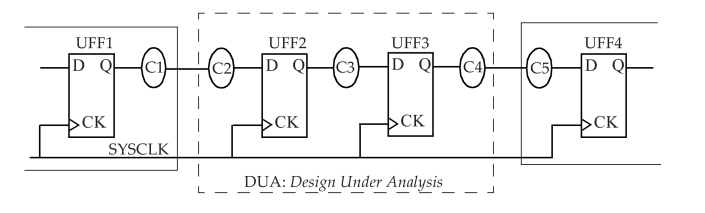

什么是STA环境?大部分数字设计是同步的,从前一个时钟周期计算出的数据在时钟有效沿上被锁存在触发器中。为了对这种设计执行STA,需要指定触发器的时钟、以及进入设计和退出设计的所有路径的时序约束。

4.1 Specifying Clocks

4.1.1(主)时钟定义

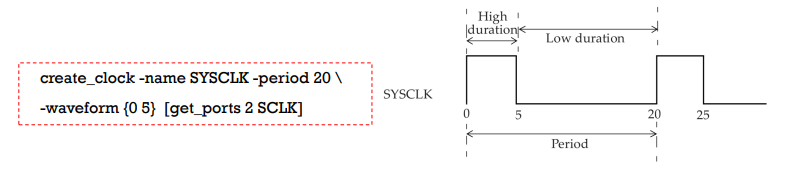

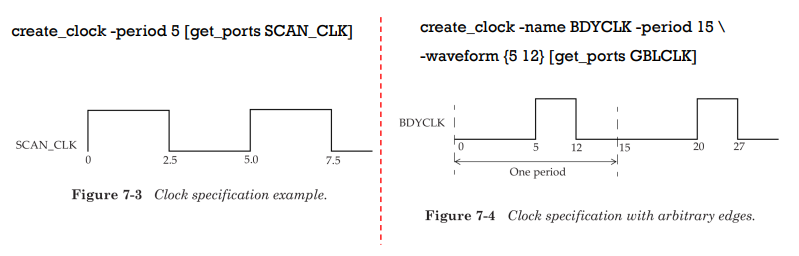

要定义时钟,我们需要提供以下信息:时钟源(Clock source)、周期(Period)、占空比(Duty cycle)边沿时间(Edge times)。

以下是一个基本的时钟约束规范:

create_clock -name SYSCLK -period 20 -waveform {0 5} [get_ports SCLK]

4.1.2.时钟不确定度(set_clock_uncertainty)

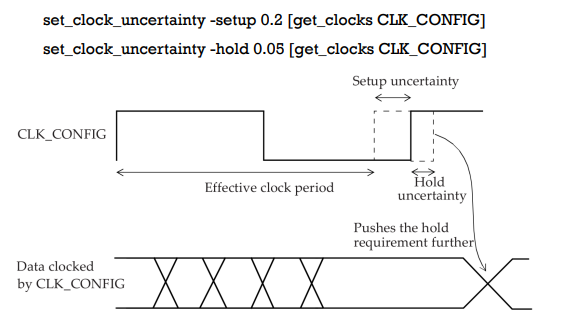

可以使用set_clock_uncertainty约束来指定时钟周期的时序不确定度(uncertainty),该不确定度可用于对可能会减少有效时钟周期的各种因素进行建模。 这些因素可能是时钟抖动(jitter)以及可能需要在时序分析中考虑的任何其它悲观度。建立时钟不确定性声明,会使整个电路的时序变得更加严苛,满足设计的稳健性。

时钟不确定性的主要来由:

时钟偏差(clock skew):时钟源到达不同触发器的时间偏差

时钟抖动(clock jitter):时钟边沿的超前或滞后

时钟延迟(clock delay):网络延迟和源延迟

对于保持时间检查,时钟不确定度将用作需要满足的额外时序裕量,如下图所示:

set_clock_uncertainty -setup 0.2 [get_clocks CLK_CONFIG]

set_clock_uncertainty -hold 0.05 [get_clocks CLK_CONFIG]

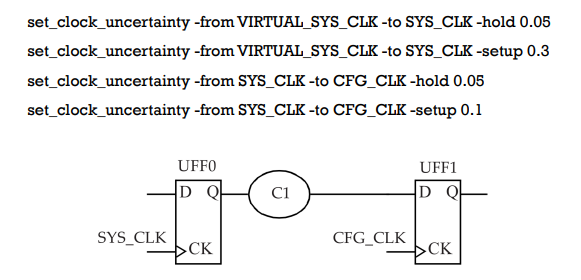

以下命令可用于指定跨时钟边界路径上的时钟不确定度:

set_clock_uncertainty -from VIRTUAL_SYS_CLK -to SYSCLK -hold 0.05

set_clock_uncertainty -from VIRTUAL_SYS_CLK -to SYSCLK -setup 0.3

set_clock_uncertainty -from SYS_CLK -to CFG_CLK -hold 0.05

set_clock_uncertainty -from SYS_CLK -to CFG_CLK -setup 0.1

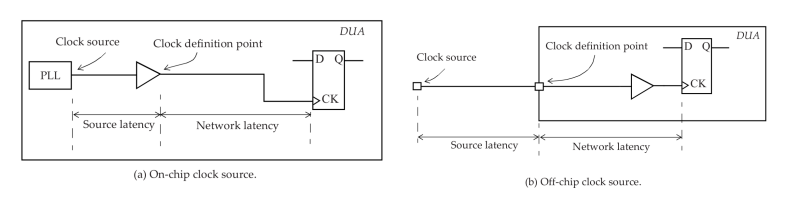

4.1.3 时钟延迟

时钟延迟分为两种类型:网络延迟(network latency)和源延迟(source latency)。网络延迟是指从时钟定义点(create_clock)到触发器时钟引脚的延迟,源延迟是指从时钟源到时钟定义点(create_clock)的延迟。具体如下图所示:

以下指令可以指定时钟的延迟:

set_clock_latency 0.8 [get_clocks CLK_CONFIG]

# Specify a network latency (no -source option) of 0.8ns for rise, fall, max and min.

set_clock_latency 1.9 -source [get_clocks SYS_CLK]

# Specify a source latency

set_clock_latency 0.851 -source -min [get_clocks CFG_CLK]

# Specify a min source latency

set_clock_latency 1.322 -source -max [get_clocks CFG_CLK]

# Specifv a max source latency

set_clock_latency 1.8 -rise [get_clocks MAIN_CLK]

# Specify a rise latency

set_clock_latency 2.1 -fall [all_clocks]

# Specify a fall latency

4.2 Generated Clocks

衍生时钟是从主时钟(master clock)派生而来的时钟