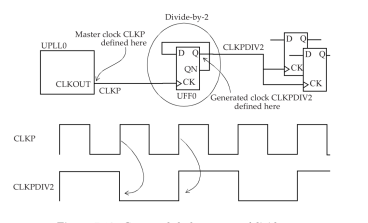

,主时钟是指使用create_clock命令定义的时钟。在基于主时钟的设计中生成一个新时钟时,可以将这个新时钟定义为衍生时钟。

例如根据一个时钟周期为10的主时钟CLKP生成一个二分频衍生时钟CLKPDIV2,指令示例如下:

create_clock -name CLKP 10 [get_pins UPLL0/CLKOUT]

#主时钟

create_generated_clock -name CLKPDIV2 -source UPPL0/CLKOUT -divide_by 2 [get_pins UFF0/Q]

#衍生时钟

可以在触发器的输出端定义一个新的时钟,即主时钟,而不是生成的时钟吗?

答案是肯定的,但是有一些缺点。定义一个主时钟而不是一个衍生时钟会创建一个新的时钟域,软件工具会当做异步时钟处理而不是同步时钟处理。将新时钟定义为衍生时钟不会创建新的时钟域,并且衍生时钟被认为与其主时钟同相,衍生时钟不需要开发额外的约束。因此,尽量将内部新生成的时钟定义为衍生时钟,而不是将其声明为另一个主时钟。

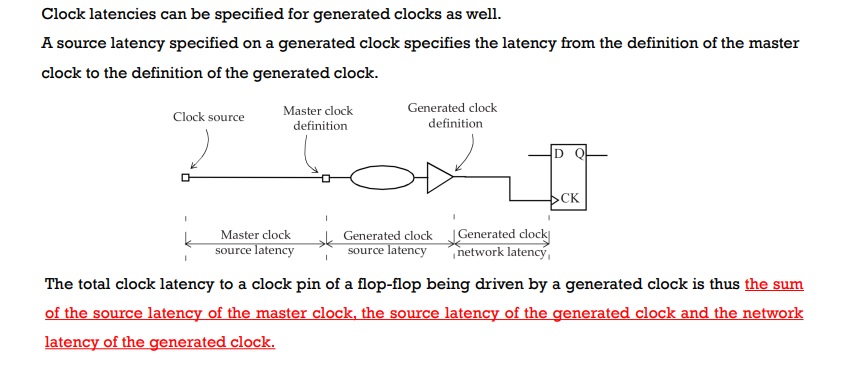

主时钟和衍生时钟之间的另一个重要区别是时钟源的概念。在主时钟中,时钟源位于主时钟的定义点。而在衍生时钟中,时钟源是主时钟的源而不是衍生时钟的源。这意味着在时钟路径报告中,时钟路径的起点始终是主时钟的定义点。这样一来,与定义新的主时钟相比,衍生时钟具有很大优势,是不会自动考虑源延迟的。因此,由衍生时钟驱动的触发器的时钟引脚的总时钟延迟是主时钟源延迟、衍生时钟源延迟和衍生时钟网络延迟的总和。如下图所示:

相反的,如果时钟操作输出的时钟和源时钟没有太多关系(不是直接的倍频分频等),失去了相位和周期的继承性,那么此时输出的时钟就是可以定义为主时钟,而非衍生时钟。

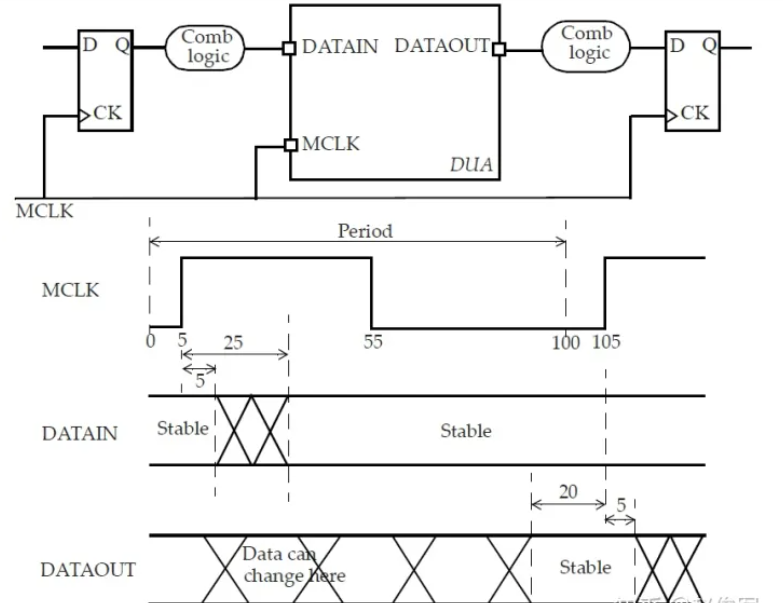

为什么需要进行输入输出路径的约束?

这里需要注意的一点是,STA无法检查不受约束的路径上的任何时序,因此需要约束所有路径以进行时序分析。输入输出路径的约束关系可以用来确定可靠地捕获DUA内部数据的可用时间。

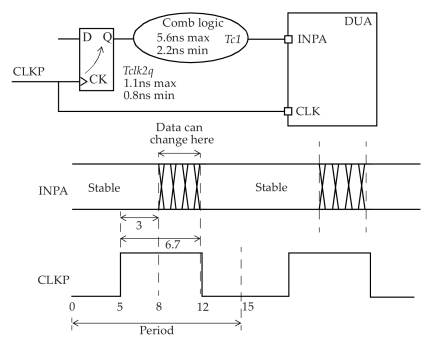

1.输入路径约束

让我们同时考虑最大和最小延迟情况,以下是输入路径的约束:

create_clock -period 15 -waveform {5 12} [get_ports CLKP]

set_input_delay -clock CLKP -max 6.7 [get_ports INPA]

set_input_delay -clock CLKP -min 3.0 [get_ports INPA]

可以通过约束关系得到:CLK到INPA的最大延迟为和最小延迟分别为6.7ns和3.0ns,已知时钟周期为15ns,则可以得到8.3ns是用来可靠地捕获DUA内部数据的可用时间。

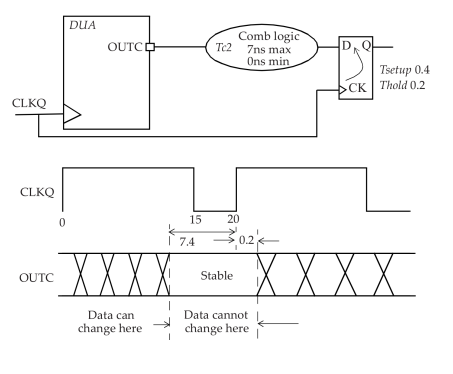

2.输出路径约束

让我们同时考虑最大和最小延迟情况,以下是输入路径的约束:

create_clock -period 20 -waveform {0 15} [get_ports CLKQ]

set_output_delay -clock CLKQ -min -0.2 [get_ports OUTC]

set_output_delay -clock CLKQ -max 7.4 [get_ports OUTC]

可以通过约束关系得到:CLKQ到OUTC的最大延迟为和最小延迟分别为7.4ns和-0.2ns,已知时钟周期为15ns,则可以得到7.6ns是OUTC必须保持稳定状态的时间。

3.输入输出路径约束

补充:

1.了解时序路径组(Timing Path Groups):由终点决定命名

2.了解外部属性建模(Modeling of External Attributes

):对于输入,需要在输入端口处指定驱动强度;对于输出,需要指定输出引脚的负载电容;

#输入驱动

set_drive 100 UCLK

set_drive -rise 3 [all_inputs]

set_drive -fall 2 [all_inputs]

#指定驱动强度,数字代表驱动电阻,电阻越小驱动强度越高,0表示无限的驱动强度

#第一种已经过时,不推荐

set_driving_cell -lib_cell INV3 -library slow [get_ports INPB]

set_driving_cell -lib_cell INV2 -library tech13g [all_inputs]

set_driving_cell -lib_cell BUFFD4 -library tech90gwc [get_ports {testmode[3]}]

#指定驱动输入端口的单元类型

#第二种功能同第一种,用法更精准更方便

set_input_transition 0.85 [get_ports INPC]

set_input_transition 0.6 [all_inputs]

set_input_transition 0.25 [get_ports SD_DIN*]

#输入端口表示过渡时间的便捷方法

#第三种更为直接,直接指定输入端口的转换时间;

#输出驱动

set_load 5 [get_ports OUTX]

set_load 25 [all_outputs]

set_load -pin_load 0.007 [get_ports {shift_write[31]}]

#输出负载影响驱动输出的单元的延迟,数值越小延迟越小

4.4 Design Rule Checks(DRC)

STA中两个常用的设计规则是最大过渡时间-max_transition和最大电容-max_capacitance。这些规则将会检查设计中的所有端口和引脚是否满足过渡时间和电容的规定约束。作为STA的一部分,任何设计规则的违例(violation)均以裕量(slack)的形式报告。这些规则可以使用以下命令指定:

set_max_transition 0.6 IOBANK

set_max_capacitance 0.5 [current_design]

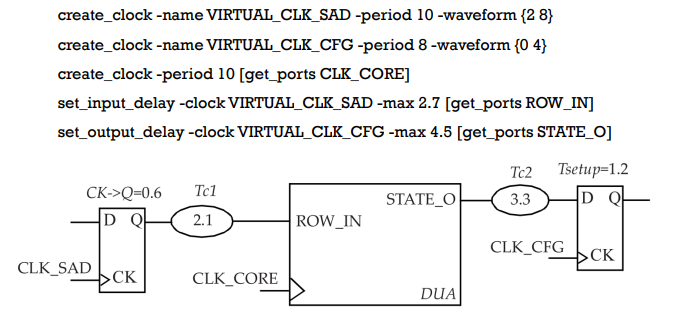

4.5 Virtual Clocks

虚拟时钟存在但是不和设计中的端口和引脚相连接。它在STA分析中用作参考,以指定相对于时钟的输入和输出延迟。

4.6 Refining the Timing Analysis

用于精细化约束分析的四个常用命令是:

set_case_analysis

#在单元的引脚或输入端口上指定常量值。

set_disable_timing

#中断单元的时序弧。

set_false_path

#指定实际不存在的路径,这意味着在STA中不需要检查这些路径。

set_multicycle_path

#指定可能花费超过一个时钟周期的路径。

1.指定无效信号

主要面临的情况是DFT、多功能模式和MUX:

1.如果芯片中具有DFT(可测性设计)逻辑,则在正常功能模式下,芯片的TEST引脚将一直为0。

2.如果设计具有多种功能模式,而只需要分析其中一种功能模式,则可以使用set_case_analysis来指定要分析的模式。

3.在MUX设计中指定set_case_analysis,分别对每个信号进行分析是十分必要的。

set_case_analysis 0 TEST

set_case_analysis 0 [get_ports {testmode[3]}]

set_case_analys