is 0 [get_ports {testmode[2]}]

set_case_analysis 0 [get_ports {testmode[1]}]

set_case_analysis 0 [get_ports {testmode[0]}]

#指定DFT端信号无效

set_case_analysis 1 func_mode[0]

set_case_analysis 0 func_mode[1]

set_case_analysis 1 func_mode[2]

#具有多功能的模块,对每个功能分别单独分析

set_case_analysis 1 UCORE/UMUX0/CLK_SEL[0]

set_case_analysis 1 UCORE/UMUX1/CLK_SEL[1]

set_case_analysis 0 UCORE/UMUX2/CLK_SEL[2]

#对MUX每个信号单独分析

2.中断单元内的时序弧

在某些情况下,单元中的一条路径可能无法发生。由于时序弧不再存在,因此需要分析的时序路径更少。

使用set_disable_timing命令需要格外小心,因为它会删除通过指定引脚的所有时序路径。在可能的情况下,最好使用set_false_path和set_case_analysis命令。

set_disable_timing -from S -to Z [get_cells UMUX0]

#直接中断时序弧

3.伪路径时序分析

指定实际不存在的路径,这意味着在STA中不需要检查这些路径。伪路径约束很重要,对于跨时钟域的模块之间的路径,不予分析。注意,伪路径约束是单向的。伪时序路径后文重点分析。

4.多周期路径时序分析

信号传输可能花费超过一个时钟周期的路径。输入到输出的延迟跨越了多个时钟周期。多周期时序路径后文重点分析。

五、时序检查

5.1 建立时间与保持时间检查方法

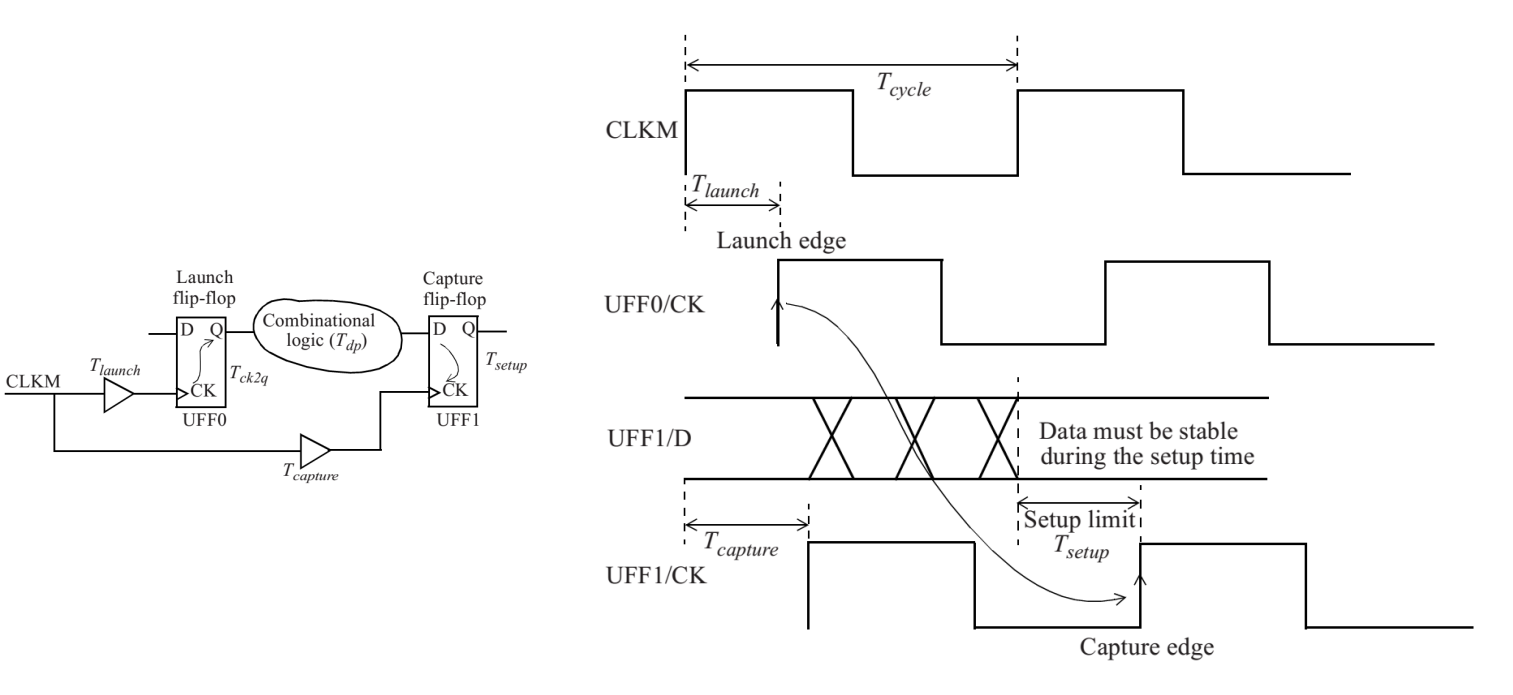

5.1.1建立时间检查

建立时间检查可以用数学公式表示:

$$T_{launch}+T_{ck2q}+T_{dp} < T_{capture}+T_{cycle}-T_{setup}$$

通常,有一个发起触发器(用于发起数据的触发器)和捕获触发器(用于捕获数据的触发器),这个捕获触发器的建立时间要求必须满足上述公式。换而言之,数据到达捕获触发器D引脚所花费的总时间必须小于时钟传输到捕获触发器所花费的时间加上时钟周期再减去建立时间要求。

由于建立时间检查受到 -max的约束,因此建立时间检查始终使用 最长或最大的时序路径。出于同样的原因,通常在 延迟最大的慢工艺角(slow corner)下执行建立时间检查。

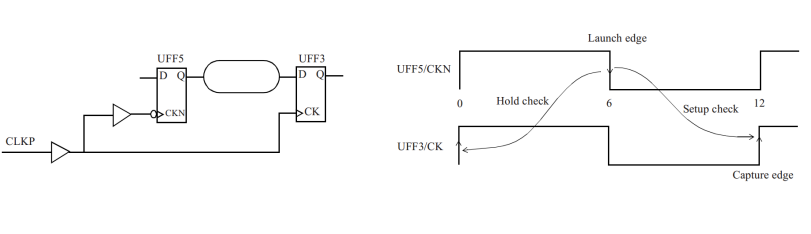

具体时序如下所示:

在前面我们知道时序路径有四种,如下为触发器到触发器的时序报告:

其他三条时序路径不再赘述,具体可查看静态时序分析圣经翻译计划――第八章:时序检查(上)

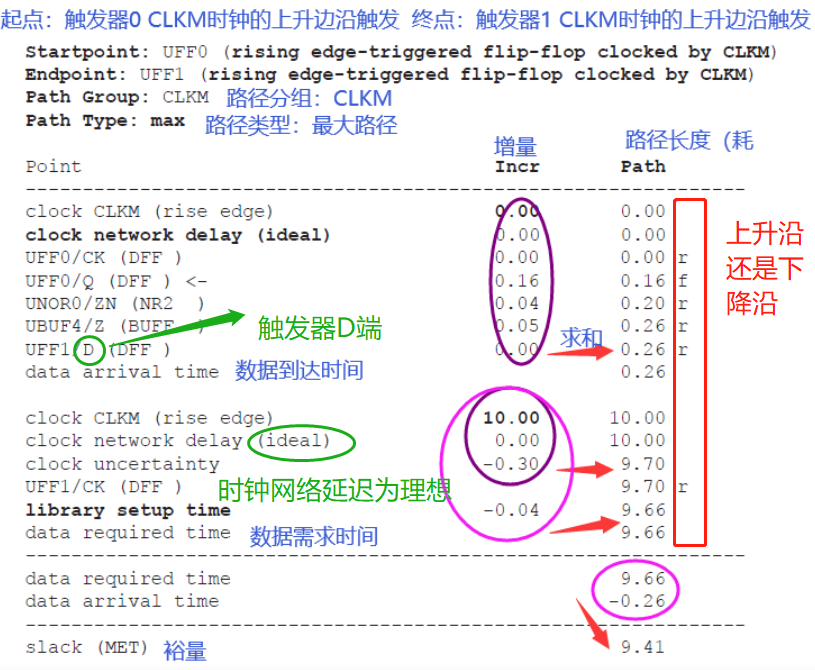

时序报告中的时钟网络延迟(clock network delay)是什么?为什么将其标记为理想(ideal)?

时序报告中的这一行表明时钟树被认为是理想的,时钟路径中的任何缓冲器(buffer)都假定为零延迟。一旦构建了时钟树,就可以将时钟网络标记为“已传播”(propagated),从而使得时钟路径显示实际延迟值,例如时序报告中所示:0.11ns延迟是发起时钟上的时钟网络延迟,而0.12ns延迟是捕获触发器上的时钟网络延迟。

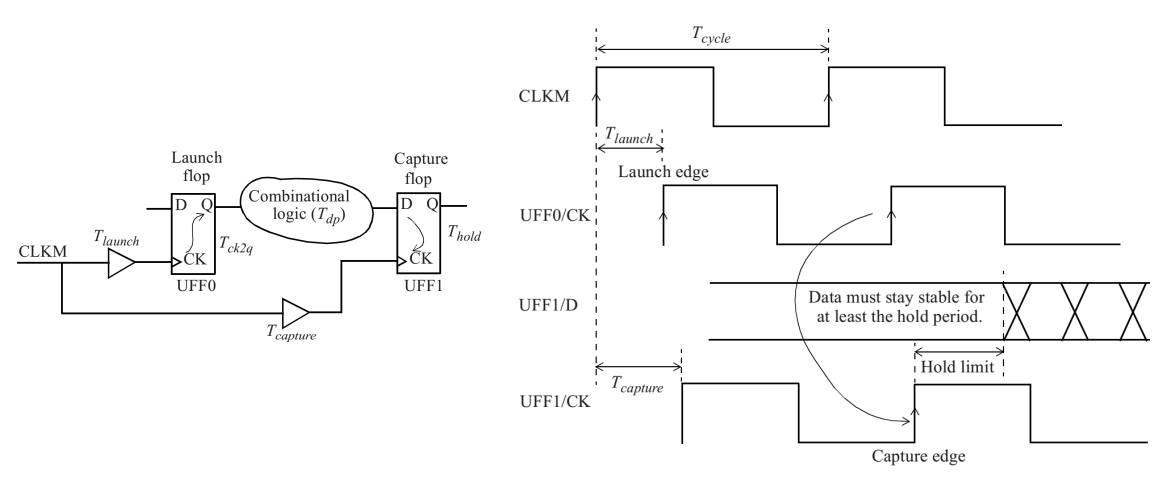

5.1.2保持时间检查

保持时间时间检查可以用数学公式表示:

$$T_{launch} + T_{ck2q} + T_{dp} > T_{capture} + T_{hold}$$

保持时间是在发起触发器(发起数据的触发器)和捕获触发器(捕获数据的触发器以及必须满足其保持时间要求的触发器)之间进行检查的,保持时间检查从发起触发器时钟的一个有效沿到捕获触发器中相同的时钟沿。因此,保持时间检查与时钟周期无关,保持时间检查会在捕获触发器时钟的每个有效沿上执行。

保持时间检查对捕获触发器的数据路径施加了最小值 -min 约束,使用 最短或最小的时序路径来进行保持时间检查,同样,在 延迟最小的快工艺角(fast corner)下执行建立时间检查。

具体时序如下所示:

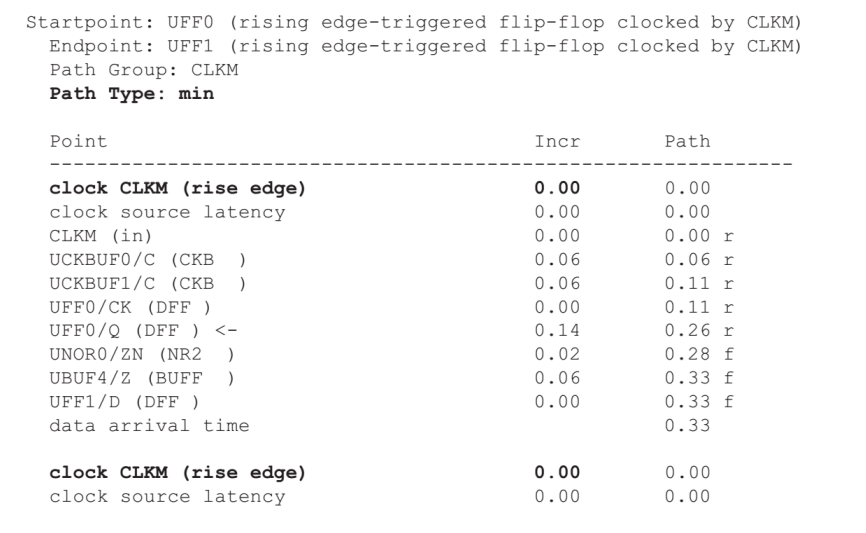

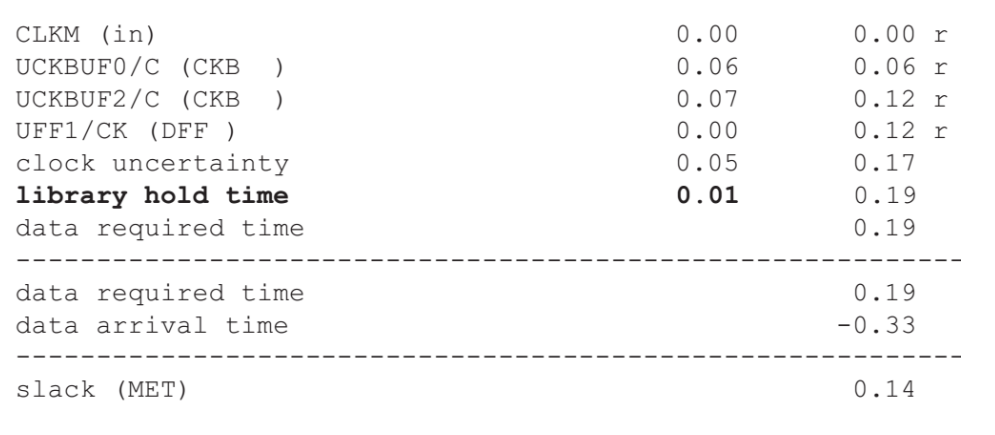

在前面我们知道时序路径有四种,如下为触发器到触发器的时序报告:

Tips:对于建立时间与保持时间的裕值slack的计算并不相同,建立时间的slack为数据需要到达时间 - 数据实际到达时间,正值则表示不违例;保持时间的slack为数据需要到达时间 - 数据实际到达时间,然后添加负号,最终正值则表示不违例。(时序报告数据实际到达时间的“-”表示此为时间为实际到达时间,计算时去绝对值即可)

5.2 多周期路径、半周期路径、伪路径时序检查

5.2.1 多周期路径检查

在某些情况下,两个触发器之间的数据路径可能需要一个以上的时钟周期才能传播通过逻辑。在这种情况下,这条组合逻辑路径会被定义为多周期路径(multicycle path)。虽然数据还是会在每个时钟沿上都被捕获触发器捕获,但我们需要告知STA在指定数量的时钟周期之后才会出现有效的捕获时钟沿。

对多周期路径进行如下约束:

create_clock -name CLKM -period 10 [get_ports CLKM]

#主时钟CLKM

set_multicycle_path 3 -setup -from [get_pins UFF0/Q] -to [get_pins UFF1/D]

#建立时间多周期约束

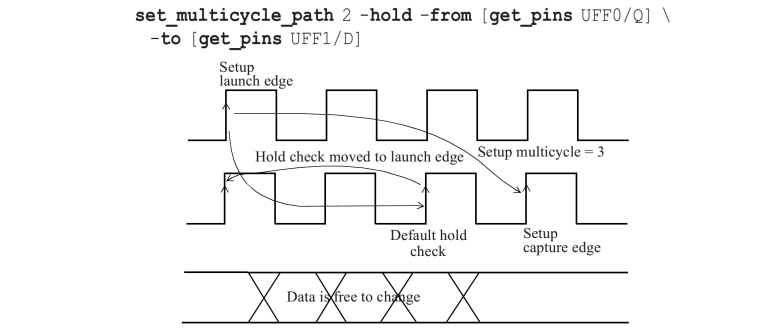

set_multicycle_path 2 -hold -from [get_pins UFF0/Q] -to [get_pins UFF1/D]

#保持时间多周期约束,将保持时间检查边沿前移两个时钟周期

Tips:如果保持时间的检查边沿没有移动到launch edge,则对于后序的保持时间要求太严苛,即数据在多周期都要求保持不变,这显然是难以实现的。只有对保持时间的检查边沿前移 N-1 个时钟周期才能更加满足时序要求。

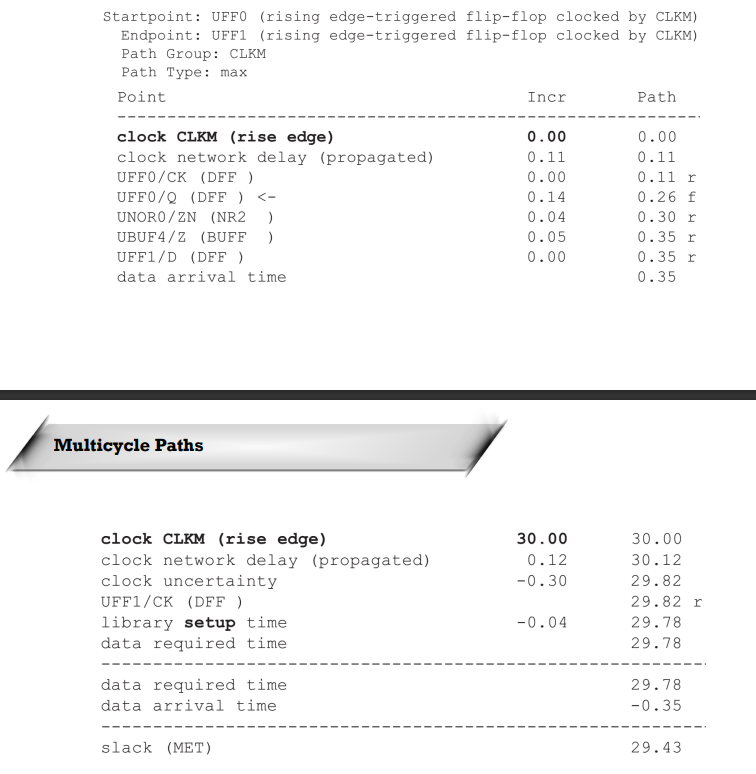

建立时间时序报告

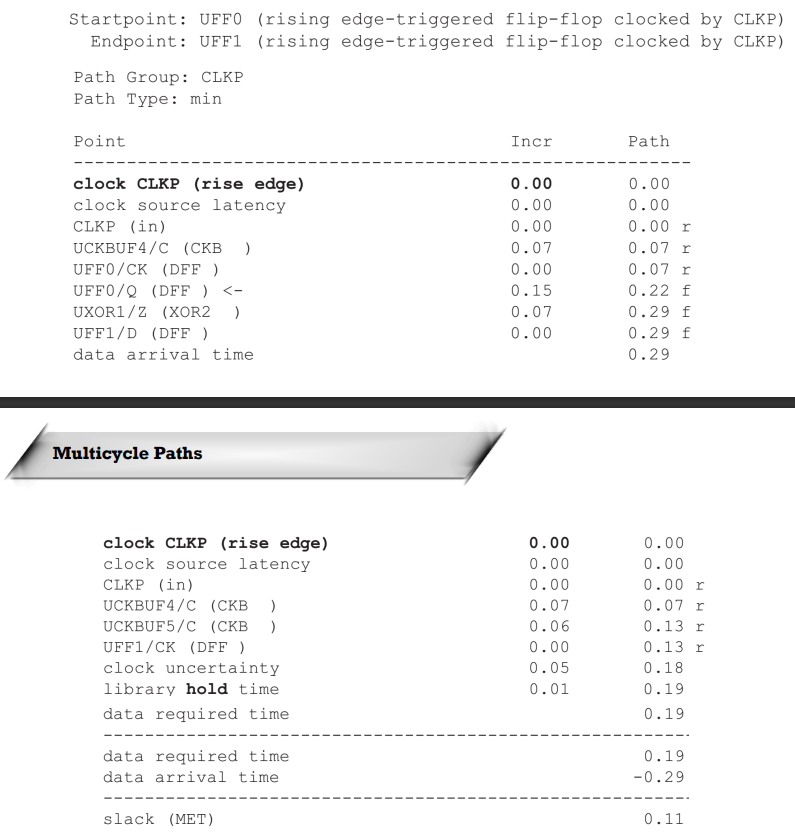

保持时间时序报告

5.2.2 半周期路径

如果设计中同时具有负边沿触发的触发器(有效时钟沿为下降沿)和正边沿触发的触发器(有效时钟沿为上升沿),则设计中可能存在半周期路径(half-cycle path)。半周期路径可能是从一个触发器的上升沿到另一个触发器的下降沿,或者反过来。半周期导致建立时间时序更加严苛,而保持时间时序更加宽松。

5.2.3 伪路径

当设计的功能运行时,某些时序路径可能不真实(或不可能)存在。在执行STA时可以将这些路径设置为伪路径(false path),这样就可以关闭这些路径,那么STA就不会对这些伪路径去进行分析了。一般来说,跨时钟域信号涉及的路径都不用STA,所以跨时钟域的路径都需要设置伪路径。

set_false_path -from [get_clocks clockA] -to [get_clocks clockB]

set_false_path -from [get_pins {regA_ * }/CK] -to [get_pins {regB_ * }/D]

set_false_path -through [get_pins UMUX0/S]

Tips:

①少用-through选项,因为会增加时序分析的复杂程度。仅在绝对有必要且没有替代方法可以指定该伪路径的情况下,才可以使用-through选项。

②尽量