直接抓取时钟,例如第一条约束与第二条约束,速度更快。

③不要将一条多周期路径约束为伪路径。

5.3 恢复时间与去除时间

恢复时间(Recovery Time):是指异步控制信号(如寄存器的异步清除和置位控制信号)在“下个时钟沿”来临之前变无效的最小时间长度。这个时间的意义是,如果保证不了这个最小恢复时间,没有给寄存器留有足够时间来恢复至正常状态,那么由于离得太近就不能保证“下个时钟沿”能正常作用导致“时钟沿”可能会失效。

去除时间(Removal Time):是指异步控制信号(如寄存器的异步清除和置位控制信号)在“有效时钟沿”之后变无效的最小时间长度。这个时间的意义是,如果保证不了这个去除时间,那么由于离得太近就不能保证有效地屏蔽这个“时钟沿”。

尤其注意,恢复时间与去除时间是针对异步控制信号而言的!如果不对异步控制信号进行 Recovery Time 和 Removal Time 时序约束,也就是说可能会造成寄存器处于不确定的状态。而这些情况是应该避免的。

Tips:单从时序的位置看,可以将恢复时间、去除时间类比为建立时间、保持时间。

5.4 跨时钟域时序

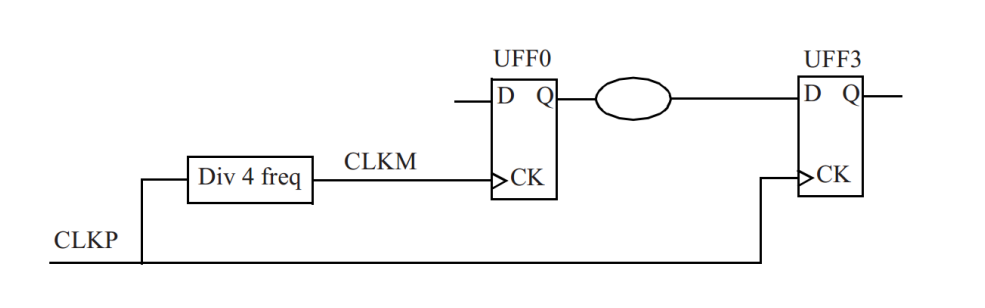

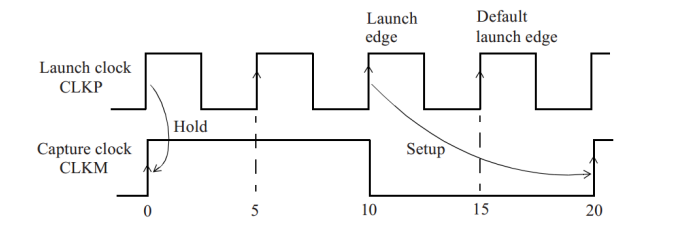

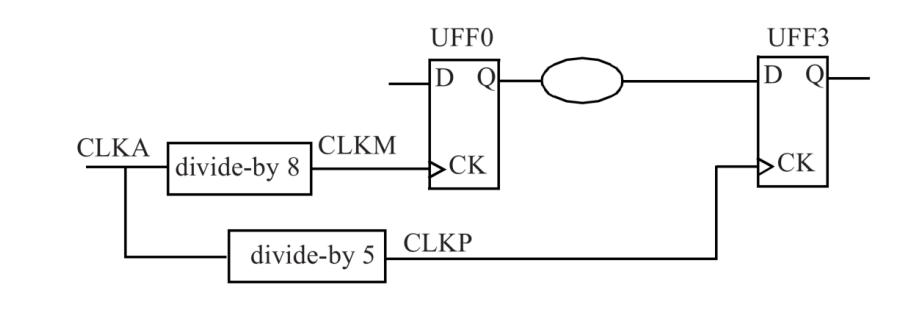

5.4.1 慢时钟域到快时钟域

时序分析一般选择最严苛的路径进行分析,最严苛的建立时间和保持时间时序如下图所示:

create_clock -name CLKM -period 20 -waveform {0 10} [get_ports CLKM]

create_clock -name CLKP -period 5 -waveform {0 2.5} [get_ports CLKP]

#时钟定义

set_multicycle_path 4 -setup -from [get_clocks CLKM] -to [get_clocks CLKP] -end

#多周期约束检查建立时间

set_multicycle_path 3 -hold -from [get_clocks CLKM] -to [get_clocks CLKP] -end

##多周期约束检查保持时间

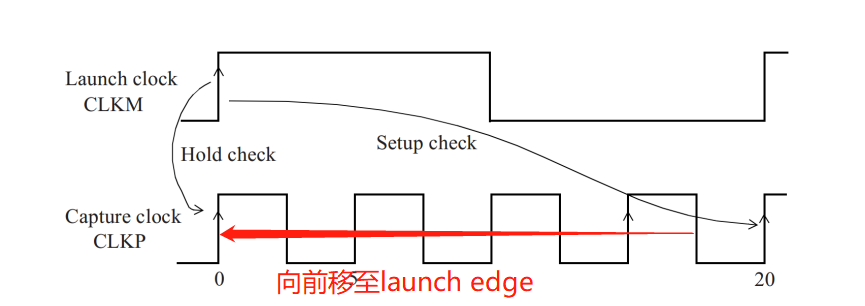

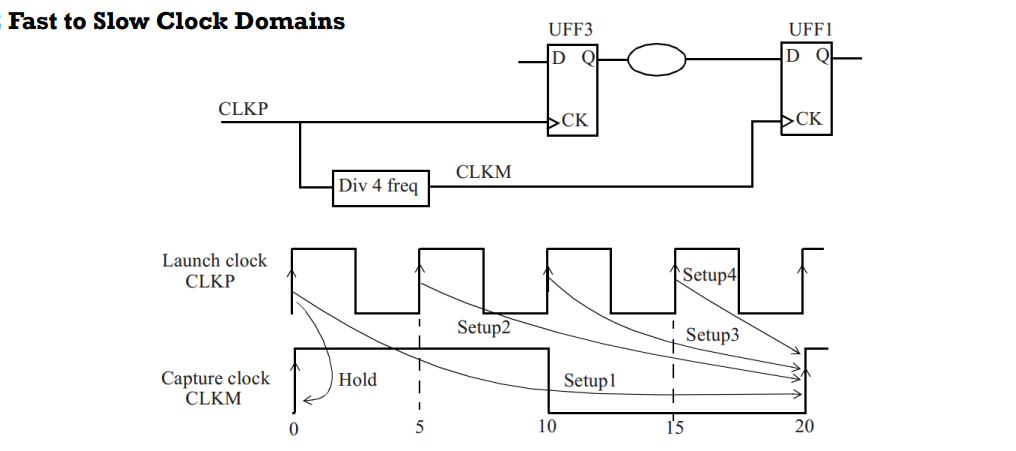

5.4 2 快时钟域到慢时钟域

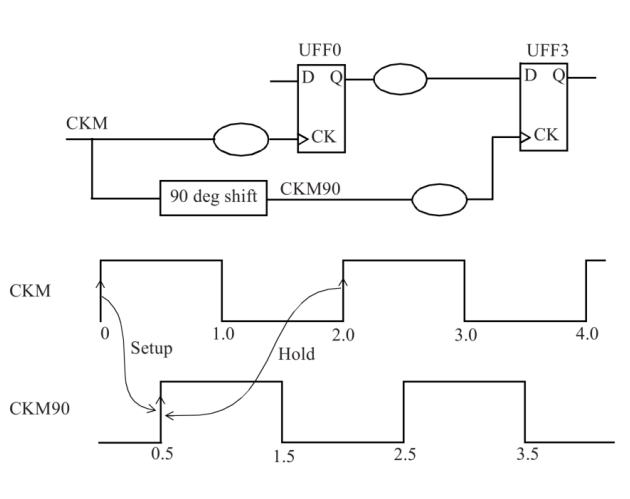

时序分析一般选择最严苛的路径进行分析,最严苛的建立时间为 Setup4,如果对时序放宽松则选择其他检查边沿,例如以 Setup2 作为检查边沿进行宽松的时序分析,建立时间和保持时间时序如下图所示:

create_clock -name CLKM -period 20 -waveform {0 10} [get_ports CLKM]

create_clock -name CLKP -period 5 -waveform {0 2.5} [get_ports CLKP]

#时钟定义

set_multicycle_path 2 -setup -from [get_clocks CLKP] -to [get_clocks CLKM] -start

#多周期约束检查建立时间

set_multicycle_path 1 -hold -from [get_clocks CLKP] -to [get_clocks CLKM] -start

#多周期约束检查保持时间

补充:选项-end是对捕获端时钟周期进行移动,-start是对发射端时钟周期进行移动。

5.5 多时钟

5.4.1 整数倍关系

参考5.3部分慢时钟域到快时钟域和快时钟域到慢时钟域

5.4.2 非整数倍关系

最重要的是找出最小公共周期!然后再将时钟扩展到该公共周期。

CLKQ和CLKP之间数据路径的公共周期仅扩展为10ns的公共周期;

CLKM和CLKQ之间数据路径的公共周期为40ns;

而CLKM和CLKP之间数据路径的公共周期也为40ns。

最严苛的建立时间检查是在时钟发起沿和捕获沿之间的最短时间内进行。最严格的保持时间检查是从0ns处的CLKM发起沿到0ns处的CLKP捕获沿。

以CLKM时钟域到CLKP时钟域的数据路径分析为例子:最严苛的建立时间检查就是24ns处的时钟CLKM发起沿以及25ns处的时钟CLKP捕获沿,最严苛的保持时间检查从0ns处的CLKM发起沿到0ns处的CLKP捕获沿。

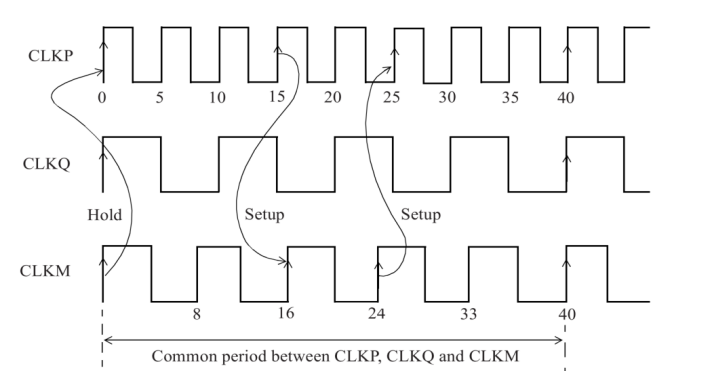

5.4.3 相移关系

建立时间:距离发射沿最近的捕获沿就是建立时间的检查边沿。

保持时间:建立时间检查的捕获边沿前一个有效边沿就是保持时间的检查边沿。

六、鲁棒性检查

本章节将介绍特殊的STA分析,例如时间借用(time borrowing)、时钟门控(clock gating)和非时序(non-sequential)检查。此外,还介绍了高级STA概念,例如片上变化(on-chip variation)、统计时序(statistical timing)以及功耗和时序之间的折中。

6.1 片上变化(OCV)

6.1.1 降额(derate)

什么是片上变化?

不同制造批次中的工艺参数差异可能会覆盖慢工艺到快工艺,而片上变化是一个芯片上的局部工艺差异和不同的电源电压和温度导致的,该差异远小于不同制造批次之间的差异(称为全局工艺差异)。因此,同一芯片的两个区域可能不在相同的PVT条件下。

为了消除或者减小片上变化,可以通过降额(derate)特定路径的延迟就可以对OCV带来的影响进行建模。

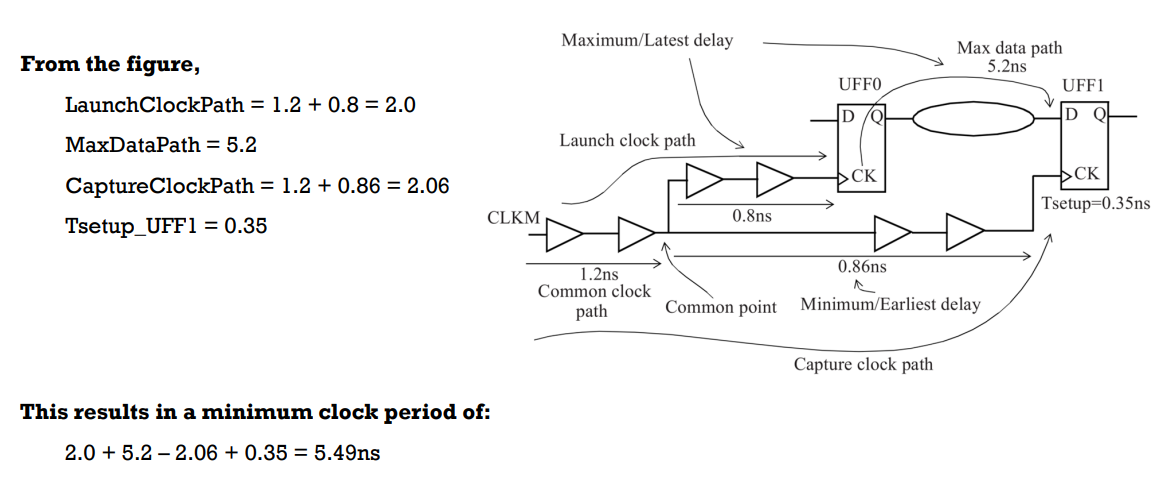

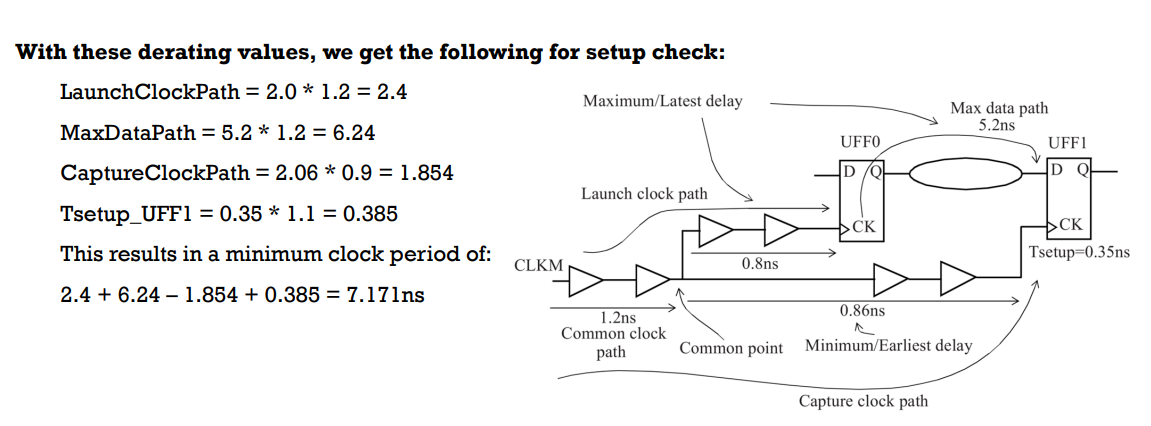

以下以建立时间时序检查为例子进行说明:

set_timing_derate -early 0.9

set_timing_derate -late 1.2

set_timing_derate -late 1.1 -cell_check

什么是early?什么是late?

对于setup Analysis:

- Launch clock: late path

- Data path: late path

- Capture clock: early path

因为 launch clock+Data path 我们都希望为latest(越late OCV越糟糕)

而 capture clock越early越糟糕(越early OCV越糟糕)

对于hold Analysis:

- Launch clock: early path

- Data path: early path

- Capture clock: late path

因为 launch clock+data path 我们都希望越early(越early OCV越糟糕)

而 capture clock 我们都希望为latest(越late OCV越糟糕)

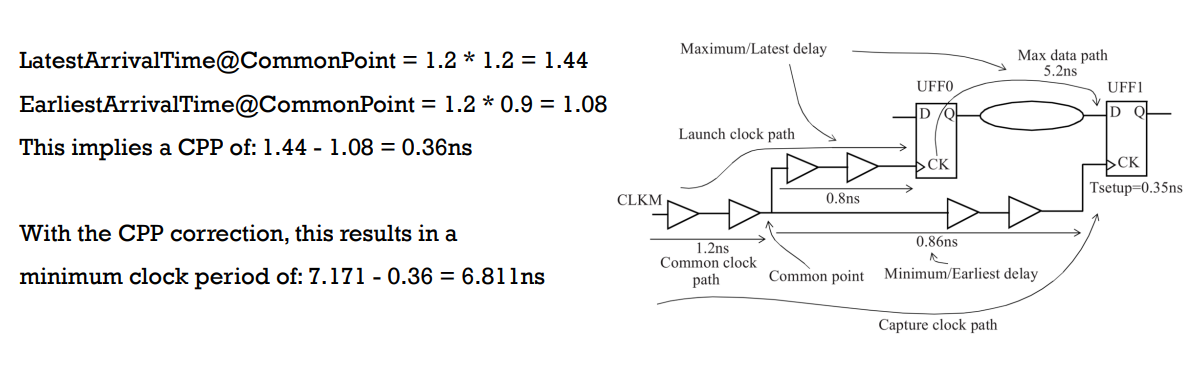

6.1.2 CPPR

由于对公共路径进行不同的derate,这明显是不合规的。CPPR(Common Path Pessimism Removal)表示“公共路径悲观度消除”,通常在路径报告中作为单独的条目列出。

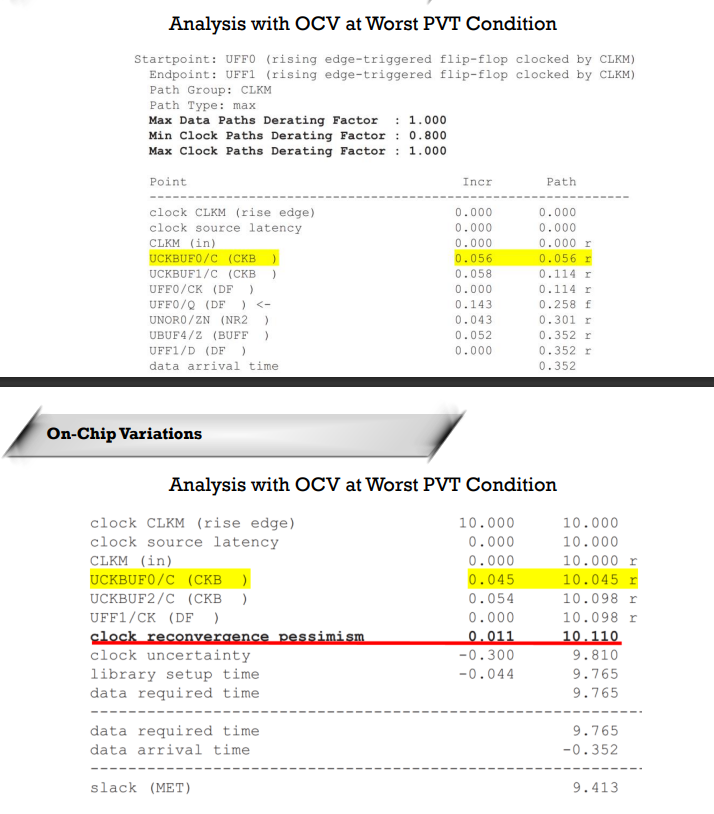

6.1.3 在最严苛的工艺下的建立时间与保持时间时序检查

1.建立时间时序检查――最差PVT条件下的OCV分析

如果在最差情况(worst-case)的PVT条件下执行建立时间检查,则在较晚路径(late path)上就无需降额了,因为它们已经是最差的情况了。但是,可以通过将特定的降额系数应用于较早路径(early path)来使那些路径更快,例如使较早路径加速10%。降额约束可能如下所示:

set_timing_derate -early 0.9

set_timing_derate -late 1.0

set_timing_derate -early 0.8 -clock

2.保持时间时序检查――最佳PVT条件下的OCV分析

通常,保持时间检查是在最佳情况的快速PVT角下执行的。在这种